Table 8-185, Serdes transmitter control register, Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 394: 1 serdes transmitter control register

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

394

Pwr = Power On Reset

Soft = Soft Reset

The Tsip2SerBlk picks the payload information from 60 TSIP-links and puts it on the 16 bit

parallel interface of the SerDes IP Block. For static test pattern transmission a supplementary

channel is provided. The supplementary channel has a data rate of 128kbit/s because of the

transmission of 16 bits every 125 μs. Furthermore the Tsip2SerBlk controls the CRC insertion

of the SerDes IP Block.

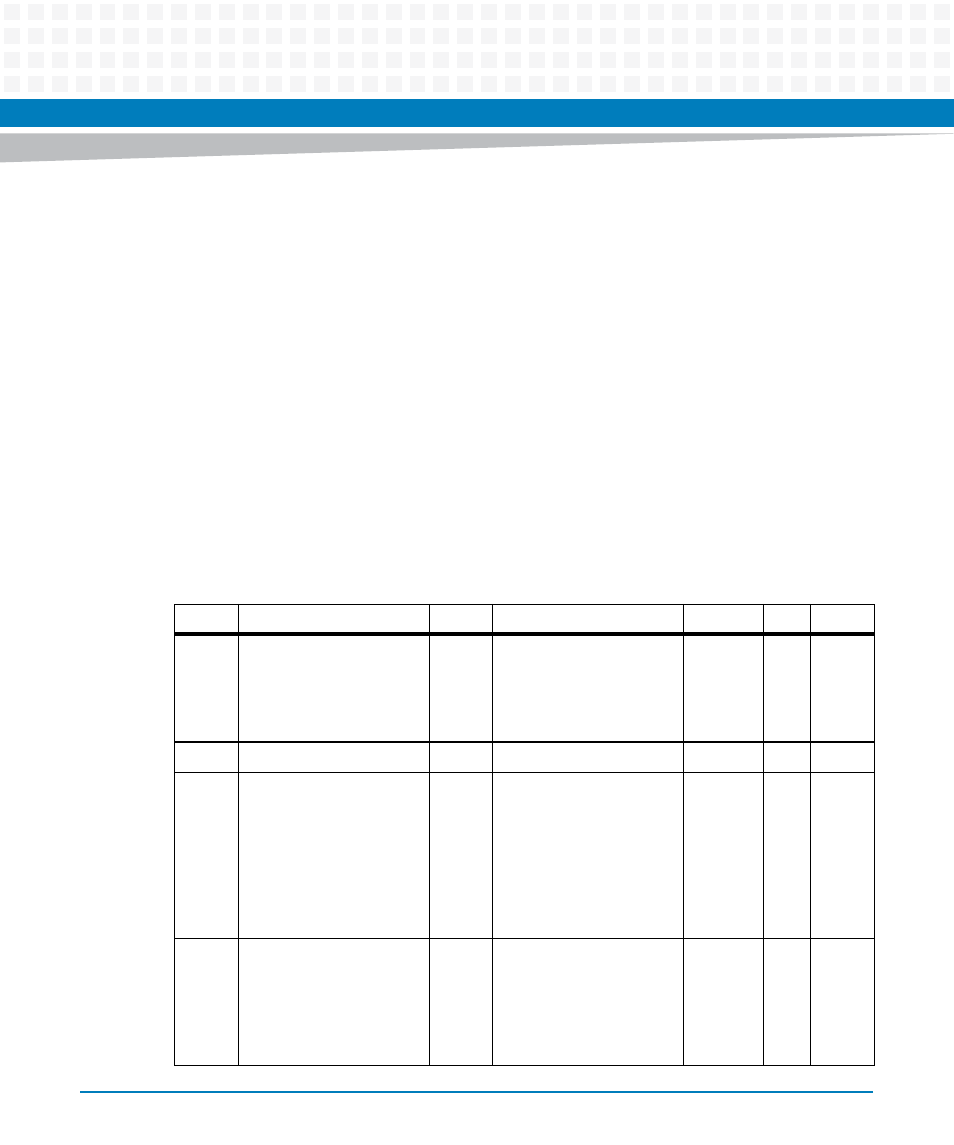

8.4.2.4.1 Serdes Transmitter Control Register

Address: 0x70, SerDesTrmCtrlReg

Width: 8 bit

A Serdes transmitter reset or resync can be initiated via this register

Table 8-185 Serdes Transmitter Control Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

7

SerdesTrmPllLolFlagReset RW

0b1:

SerdesTrmPllLolFlagReset

, resets the loss of lock

flag bit in

SerDesTrmStatReg

0b0

X

X

6...2

-

-

reserved

undef

-

-

1

SerdesTrmResync

RW

0b1: SerdesTrmResync,

Serdes transmitter sends

resync pattern sequence,

1 to 0 transition starts

sending of sequence,

data is sent automatically

after the sequence has

ended

0b0

X

X

0

SerdesTrmReset

RW

0b1: SerdesTrmReset,

puts the Serdes

transmitter into reset,

resync sequence is sent

automatically when

deactivated

0b0

X

X