1 reset types, 1 gpp-reset, Table 4-9 – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 100: Resets, Functional description

Functional Description

ATCA-8310 Installation and Use (6806800M72E)

100

Similar to the power domains, the reset is also divided into domains. This means that the SPP

and GPP can be reset independently. This is achieved by routing the Face plate Reset Key and

the RTM Reset Key over the Glue Logic FPGA. The configuration of the FPGA determines the

Reset that is asserted.

The default configuration is that SPP and GPP are reset simultaneously.

4.9.1

Reset Types

4.9.1.1

GPP-Reset

4.9.1.1.1 Cold Reset

During a Cold reset the CPU RESET#, PCI_RST# (legacy PCI bus) and PLT_RST# (downstream

PCIe busses) signals are asserted. CPU RESET# is used to reset all internal registers, state

machines and caches of the processor. The PCI_RST#/PLT_RST# is used to reset all onboard

PCI/PCIe participants of all onboard PCI/PCIe busses. The P4080 is also reset by the PLT_RST#

signal and generates CPU RESET# to the Nehalem-EP processors.

4.9.1.1.2 Warm Reset

During a Warm Reset the P4080 asserts the INIT# signal for 16 processor clock cycles. The INIT#

signal is fed to the P4080 which resets the processors through QOI messaging without

affecting its internal caches or bus state machines. Example for a Soft Reset is the Southbridge

CF9h Warm Reset.

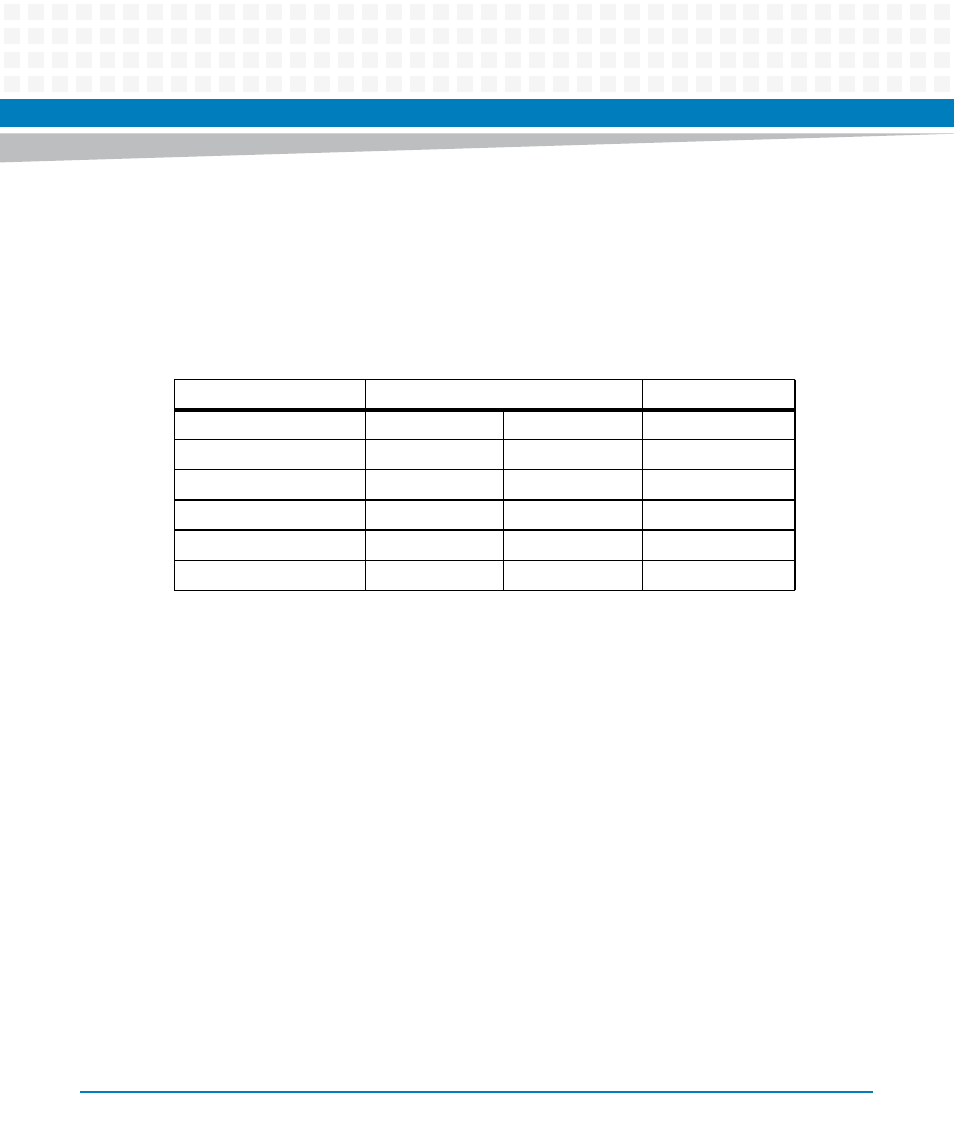

Table 4-9 Resets

Source

Cold Reset

Warm Reset

Power-Up Reset

X

X

Software Control Reset

X

X

X

Watchdog Reset

X

X

Face plate Reset Key

X

X

RTM Reset Key

X

X

IPMI Reset

X

X