Table 8-222, Configuration prom update data register, Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 426: 2 configuration prom update data register

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

426

8.4.2.10.2 Configuration Prom Update Data Register

Address: 0xD9, CfgPrmUpdDatReg

Width: 8 bit

Holds the write data to sent to the FPGA serial configuration prom when written and the read

data received from the FPGA serial configuration prom when read.

1

ReadCmdSelect

R

Read type of read command for

SPI-flash

0b1: SpiReadTypeStandard,

Standard Spi read command is

used

0b0: SpiReadTypeFast, Fast Spi

read command is used

-

-

-

0

SpiCsSet

RorW

Chip Select at SPI interface to

serial configuration prom

0b1: SpiCsSetHigh, Write: Drive

SPI Chip Select line high

0b0: SpiCsSetLow, Write: Drive

SPI Chip Select line low, possible

only if enabled by CodePrgIfEn

0b0: SpiCsIsHigh, Read: Status of

SPI Chip Select line is high

0b0: SpiCsIsLow, Read: Status SPI

Chip Select line is low

0b1

X

X

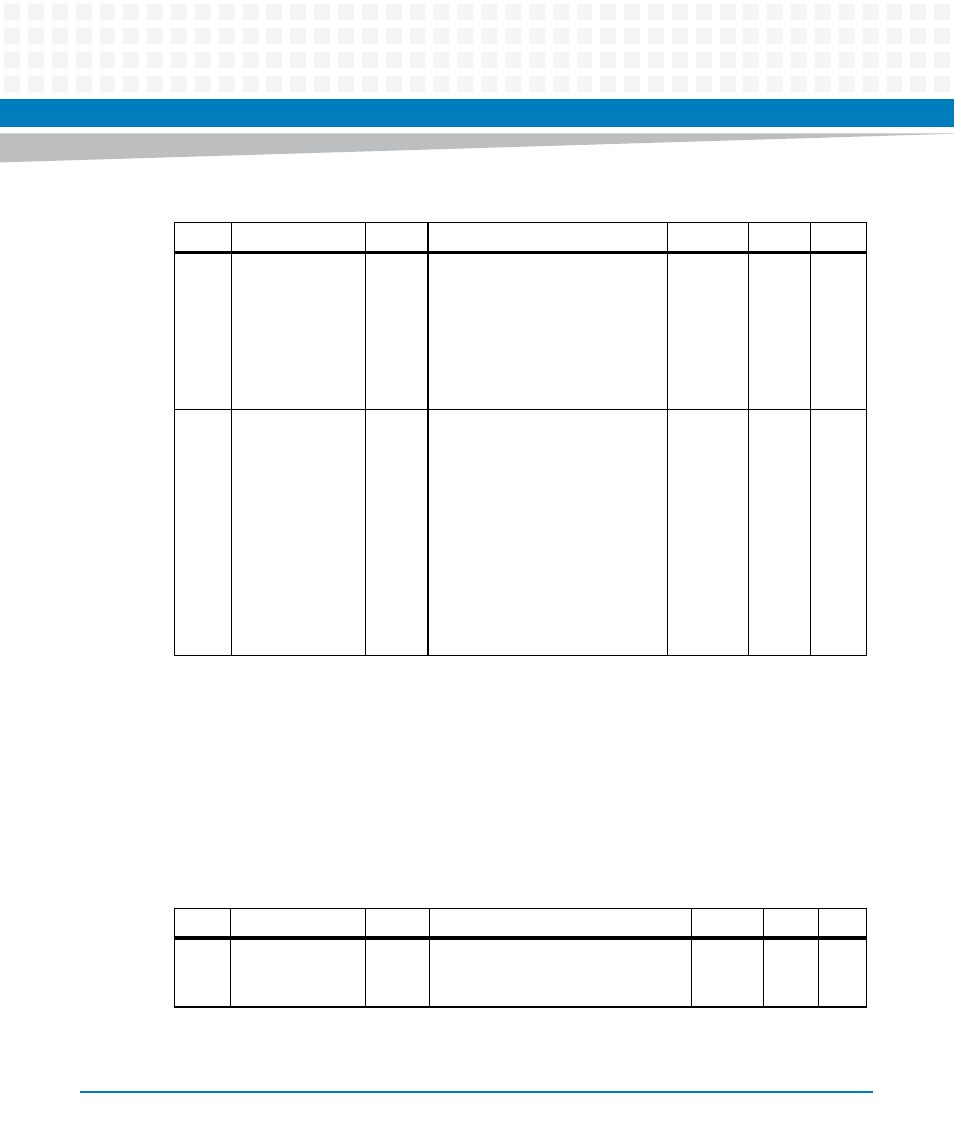

Table 8-221 Configuration Prom Update Control Register (continued)

Bit

Acronym

Type

Description

Default

Pwr

Soft

Table 8-222 Configuration Prom Update Data Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

7...0

CfgSerialPrmDat

RorW

A write triggers 8 SPI clocks and

shifts the data out to MOSI. The Data

on MISO is shifted in.

0x0

X

X