2 dsp fpga registers detailed description, Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 384

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

384

8.4.2

DSP FPGA Registers Detailed Description

Keys:

Access types:

R = Read

W = Write

RW = Write and Read back exactly what was written last time

RorW = Write one value, eg. transmit data or read other value, eg. receive data

RandC = Read and Clear specified bits automatically

Default:

Binary(0b) or hex(0x) value the respective bits are set to, when one of the reset conditions in

the following colums occurs or

- = if nothing is stored, thus nothing can be reset

undef = undefined or

const = containing a constant value not affected by any reset.

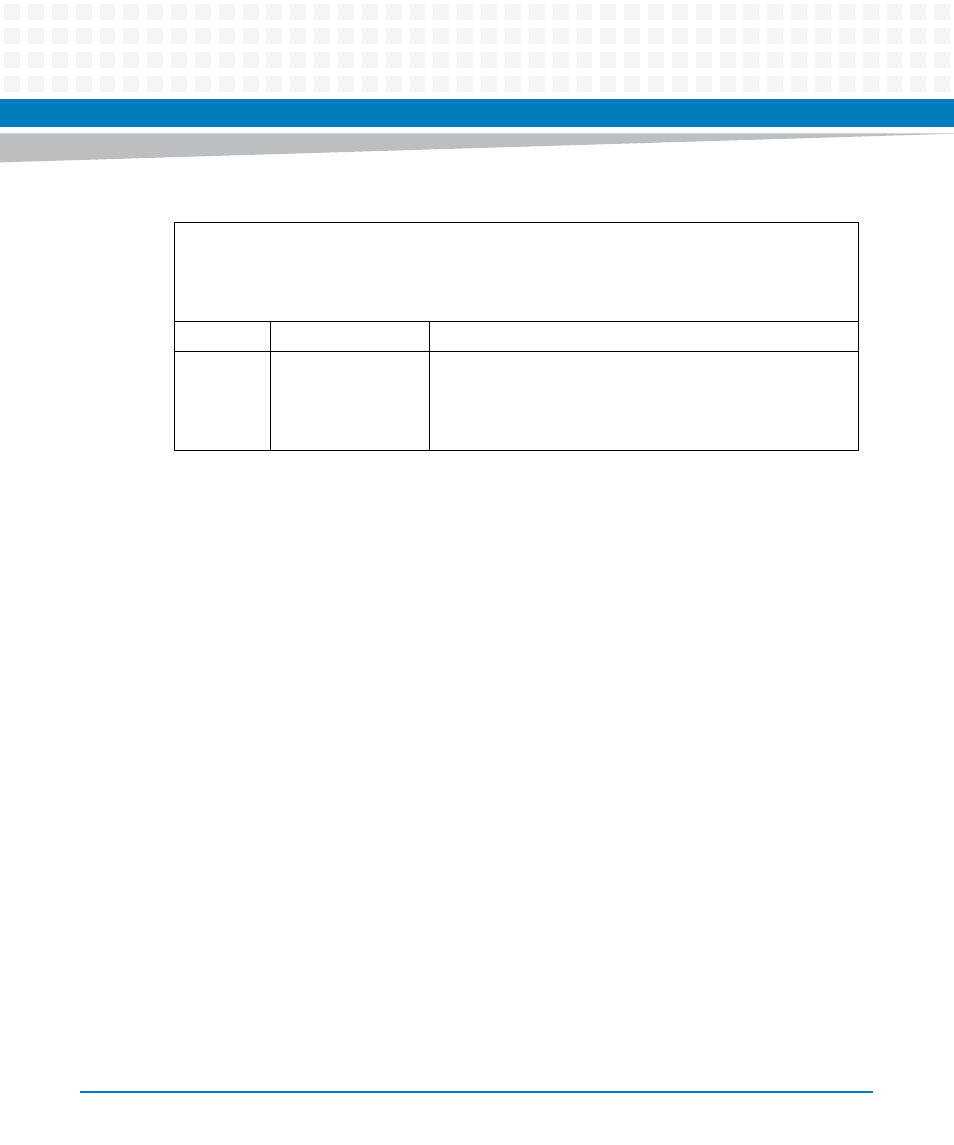

MDIO interface to Phy (MdioIfToPhy) [Hw: Cy0]

The phy can be accessed via MDIO bus through this register with a simple bit bang interface.

Access via SPI- bus from GlueFpga (occupies 256 Byte addressarea), hereof assigned to this block:

FC...FF

Address

Acronym

Description

0xFC

MdioBitBang

MDIO Bit Bang Register (8bit ) [Hw: syn , WAck1 , RAck1]

Allows to control and to read the status of an MDIO bus to the

rPhy.

Table 8-174 Logic DSP FPGA Register Overview (continued)