13 mdio interface to phy (mdioiftophy), Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 431

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

431

8.4.2.13 MDIO interface to Phy (MdioIfToPhy)

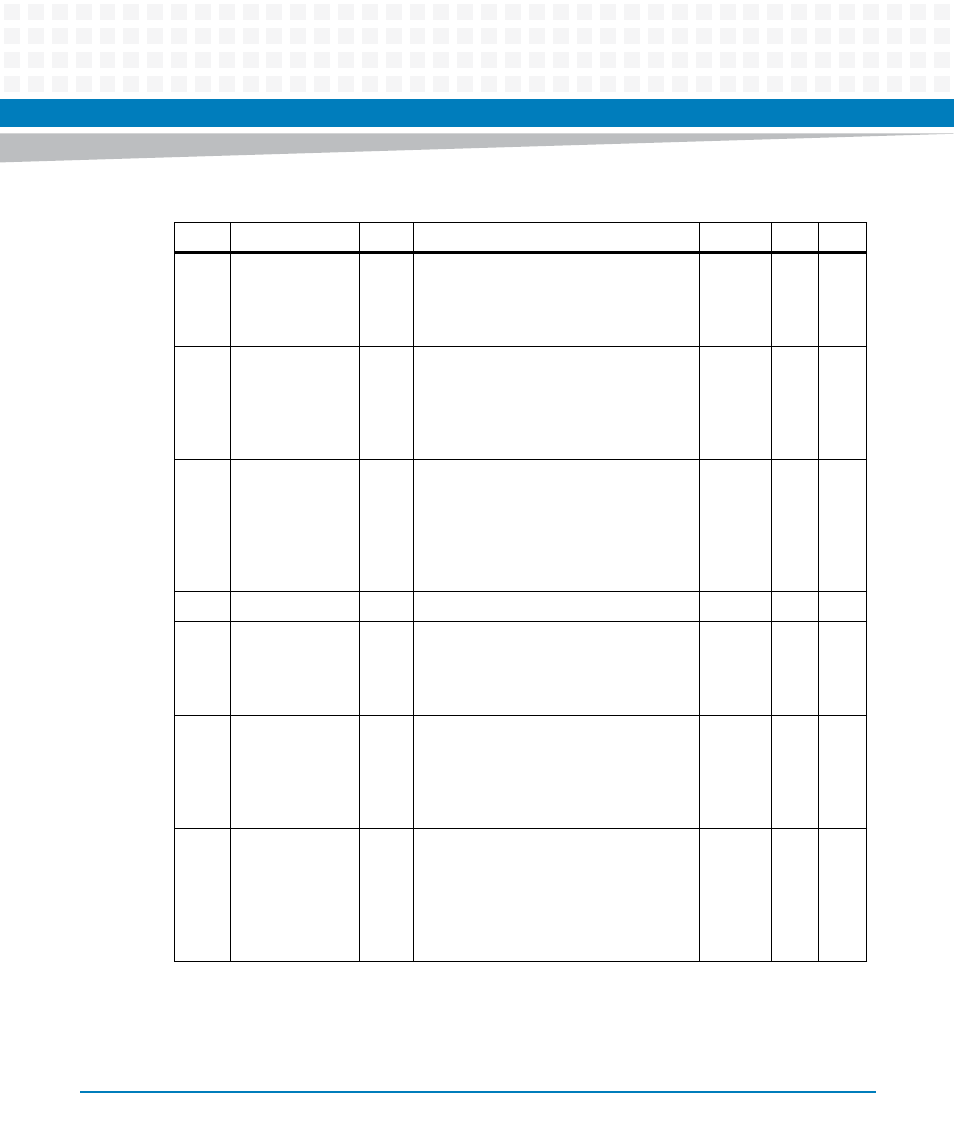

Resets:

6

SdaRead

R

0b1: SdaReadHigh, if Sda line (Data) of

I2c is high

0b0: SdaReadLow, if Sda line (Data) of

I2c is low

undef

F

F

5

SdaDirSet

RW

0b1: SdaAsOutputSet, Sda line (Data) of

I2c is driven by Dsp Fpga

0b0: SdaAsInputSet, Sda line (Data) of

I2c is not driven by Dsp Fpga, thus data

from dsp can be read

0b0

X

X

4

SdaValIfOutSet

RW

0b1: SdaValSetHigh, Sda line (Data) of

I2c is driven high by Dsp Fpga if direction

is set as output

0b0: SdaValSetLow, Sda line (Data) of

I2c is driven low by Dsp Fpga if direction

is set as output

0b0

X

X

3

-

-

reserved

undef

-

-

2

SdcRead

R

0b1: SdcReadHigh, if Sdc line (Clock) of

I2c is high

0b0: SdcReadLow, if Sdc line (Clock) of

I2c is low

undef

F

F

1

SdcDirSet

RW

0b1: SdcAsOutputSet, Sdc line (Clock)

of I2c is driven by Dsp Fpga

0b0: SdcAsInputSet, Sdc line (Clock) of

I2c is not driven by Dsp Fpga, thus data

from dsp can be read

0b0

X

X

0

SdcValIfOutSet

RW

0b1: SdcValSetHigh, Sdc line (Clock) of

I2c is driven high by Dsp Fpga if direction

is set as output

0b0: SdcValSetLow, Sdc line (Clock) of

I2c is driven low by Dsp Fpga if direction

is set as output

0b0

X

X

Table 8-227 I2C Bit Bang Register (continued)

Bit

Acronym

Type

Description

Default

Pwr

Soft