Table 8-85, Spp watchdog trigger register, Table 8-86 – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 309: Gpp watchdog trigger register, Table 8-87, Spp watchdog control register, Cpld and fpga, 16 gpp/spp watchdog registers

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

309

8.2.2.3.16 GPP/SPP Watchdog Registers

SPP and SPP have each their own watchdog registers. Because the CPUs can only access its own

watchdog registers, the watchdog registers of SPP and GPP are mapped to the same address

range.

The Watchdog granularity is 1 ms. The programmable maximum time-out is 271.359 s.

The Watchdog may be disabled during Debugging when the switch SW_[7] (SW6 Pin 4) is

closed.

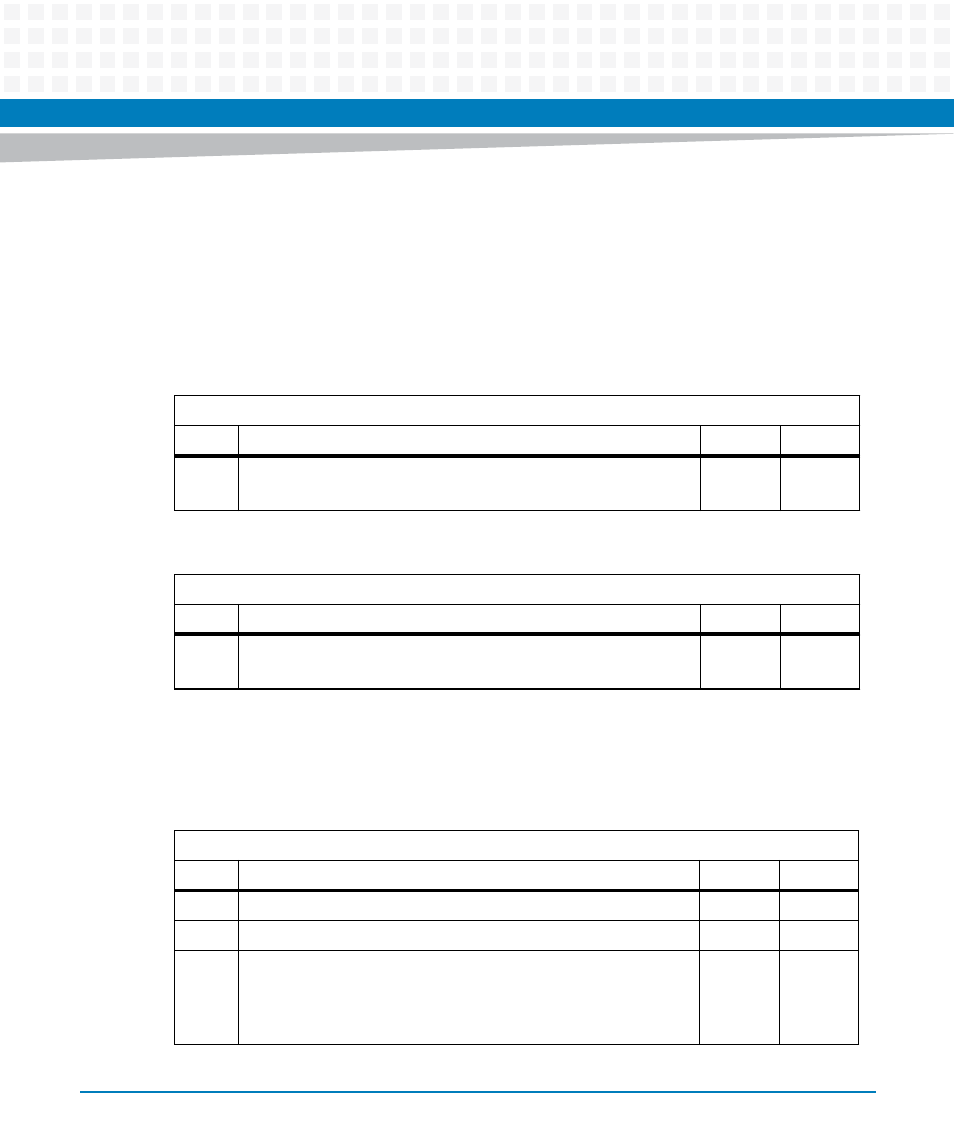

Table 8-85 SPP Watchdog Trigger Register

Address: 0x018

Bit Description

Default

Access

7:0

Trigger Watchdog.

Load 18 Bit Time-out value and (re)start watchdog.

-

SPP: w

Table 8-86 GPP Watchdog Trigger Register

Address: 0x018

Bit Description

Default

Access

7:0

Trigger Watchdog.

Load 18 Bit Time-out value and (re)start watchdog.

-

GPP: w

Table 8-87 SPP Watchdog Control Register

Address: 0x19

Bit Description

Default

Access

1:0

Most significant bits of Watchdog time-out value.

2b11

SPP: r/w

6:2

Reserved

0

r

7

Watchdog Enable

Once the Watchdog is enabled the Watchdog stays enabled until

PWR_GOOD is deassserted or SPP is reset. Watchdog time-out

may still be changed.

0

SPP:

r/w1s