Table 8-204, Dsp watchdog interrupt status reset register, Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 410: 5 dsp watchdog interrupt status reset register

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

410

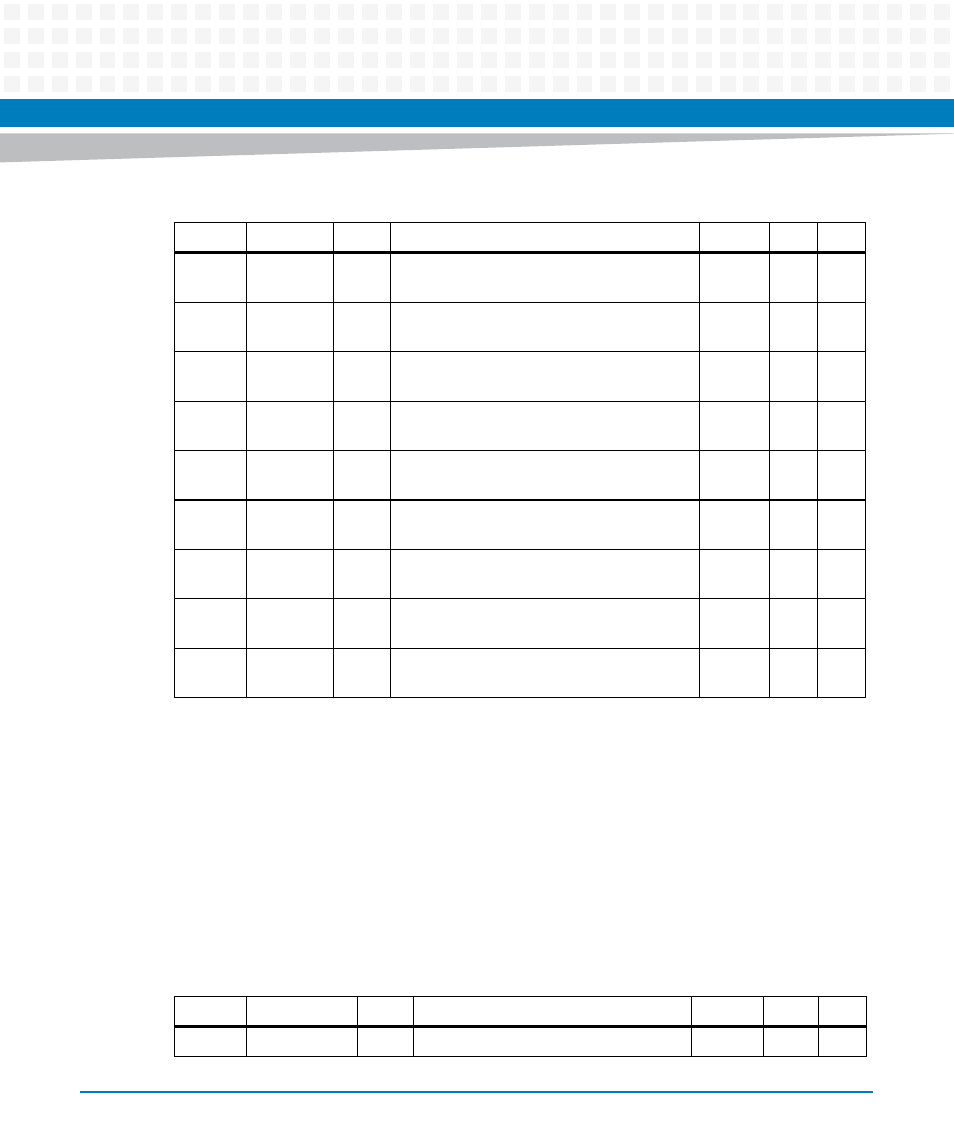

8.4.2.7.5 DSP Watchdog Interrupt Status Reset Register

Address: 0xA8, DspWdgStaResReg

Width: 16 bit

The bits of this register reset the respective bits in DspWdgStaReg. Writing a 1 to a bit in

DspWdgStaResReg resets the corresponding bit in DspWdgStaReg. The interrupt bit in

DspWdgStaReg is kept reset until writing a 0 to the corresponding bit in DspWdgStaResReg

reenables its monitor function again.

8

DspHev8

R

0b1: DspHev8, active if DSP8 has signaled a

Host Event interrupt to the Control Unit

0b0

F

F

7

DspHev7

R

0b1: DspHev7, active if DSP7 has signaled a

Host Event interrupt to the Control Unit

0b0

F

F

6

DspHev6

R

0b1: DspHev6, active if DSP6 has signaled a

Host Event interrupt to the Control Unit

0b0

F

F

5

DspHev5

R

0b1: DspHev5, active if DSP5 has signaled a

Host Event interrupt to the Control Unit

0b0

F

F

4

DspHev4

R

0b1: DspHev4, active if DSP4 has signaled a

Host Event interrupt to the Control Unit

0b0

F

F

3

DspHev3

R

0b1: DspHev3, active if DSP3 has signaled a

Host Event interrupt to the Control Unit

0b0

F

F

2

DspHev2

R

0b1: DspHev2, active if DSP2 has signaled a

Host Event interrupt to the Control Unit

0b0

F

F

1

DspHev1

R

0b1: DspHev1, active if DSP1 has signaled a

Host Event interrupt to the Control Unit

0b0

F

F

0

DspHev0

R

0b1: DspHev0, active if DSP0 has signaled a

Host Event interrupt to the Control Unit

0b0

F

F

Table 8-203 DSP Host Event Interrupt Status Register (continued)

Bit

Acronym

Type

Description

Default

Pwr

Soft

Table 8-204 DSP Watchdog Interrupt Status Reset Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

15...10

-

-

reserved

undef

-

-