Table 8-58, Modem control register (mcr), Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 284

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

284

This 8-bit register controls the interface with the modem or data set (or a peripheral device

emulating a modem).

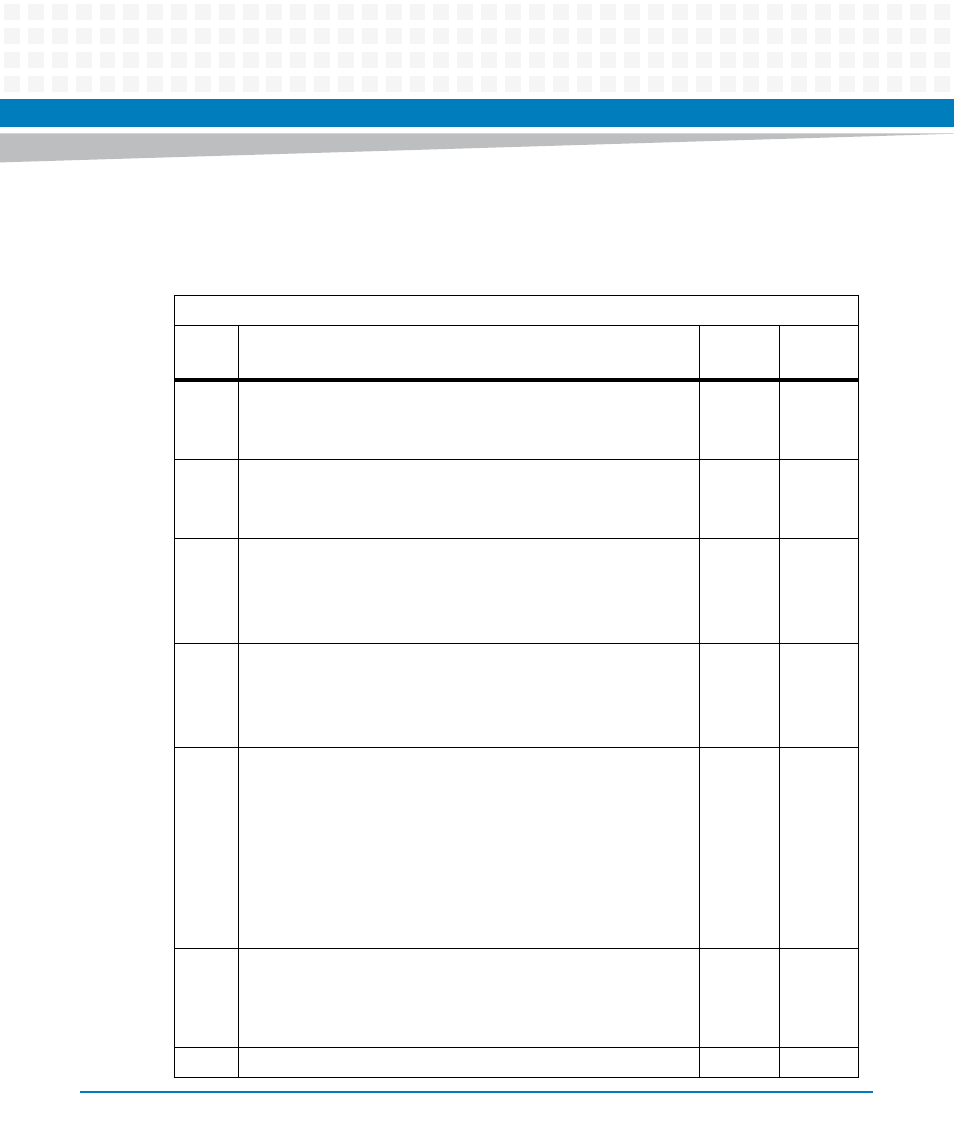

Table 8-58 Modem Control Register (MCR)

IO Address: Base + 4

Bit

Description

Default

Access

0

Data terminal ready (DTR#) output control:

1: DTR# output in low (active) state

0: DTR# output in high state

0

GPP: r/w

1

Request to send (RTS#) output control:

1: RTS# output in low (active) state

0: RTS# output in high state

0

GPP: r/w

2

User output control signal (OUT1#):

1: OUT1# output in high state

0: OUT1# output in low state

Not supported

0

GPP: r/w

3

User output control signal (OUT2#):

1: OUT2# output in high state

0: OUT2# output in low state

Not supported

0

GPP: r/w

4

Local loop back diagnostic control

When loop back is activated: Transmitter TXD is set high. Receiver

RXD is disconnected. Output of Transmitter Shift register is looped

back into the receiver shift register input. Modem control inputs

are disconnected Modem control outputs are internally connected

to modem control inputs. Modem control outputs are forced to

the inactive (high) levels:

1: Loop back mode activated

0: Normal operation

0

GPP: r/w

5

Autoflow control enable (AFE):

1: Autoflow control enabled (auto-RTS# and auto-CTS# or auto-

CTS# only enabled)

0: Autoflow control disabled

0

GPP: r/w

7:6

Reserved

0

r