Table 8-174, Logic dsp fpga register overview, Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 373

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

373

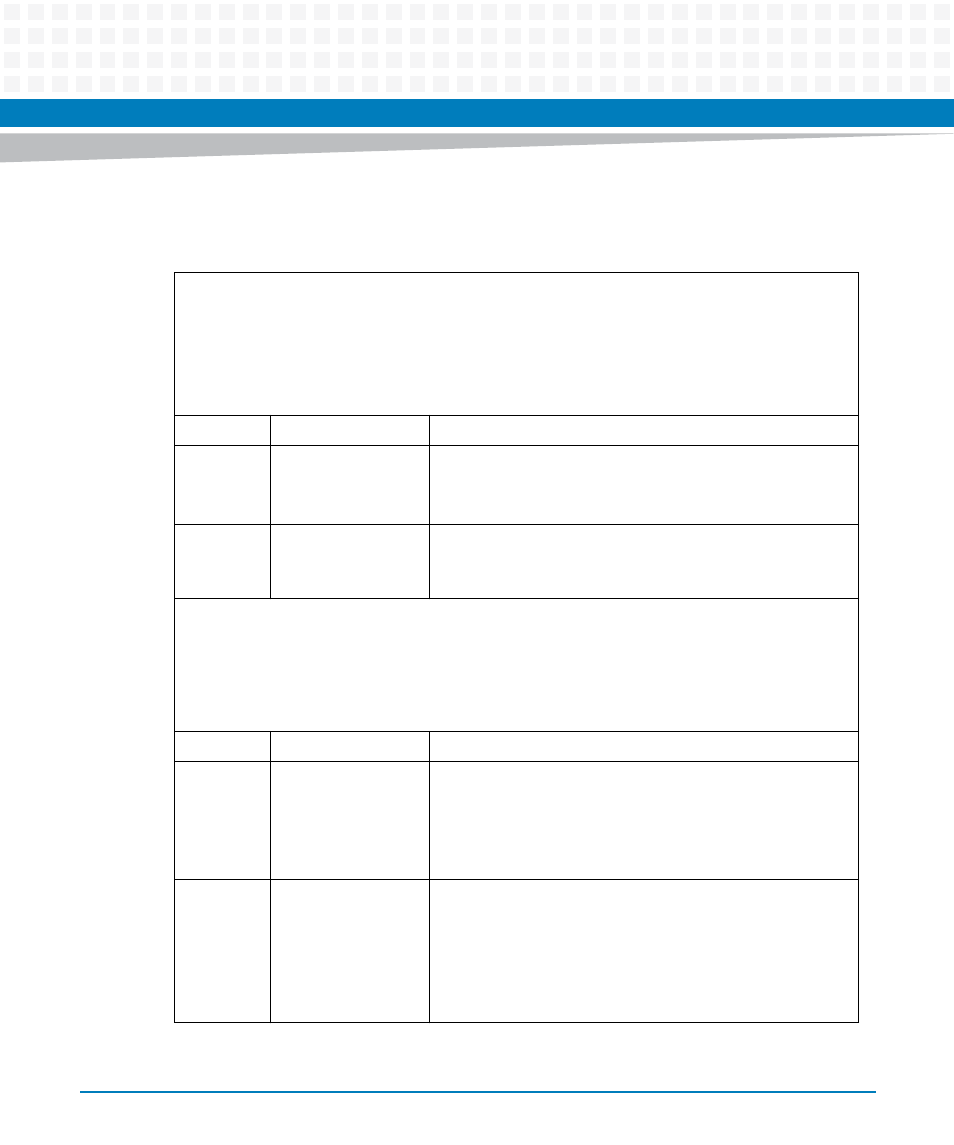

Table 8-174 Logic DSP FPGA Register Overview

SerDes Client Interface ( 8bit each ) (SerDesClientIf) [Hw: Cy0]

Provides register access to the SerDes client interface block as defined by Lattice.

Higher addresses are determined by SerDesPreselect Register. Control by SW or JTag via Orcastra is

determined.

Access via SPI- bus from GlueFpga (occupies 256 Byte address area), hereof assigned to this block:

00...4F

Address

Acronym

Description

0x0

...

0x3F

SerDesClientRegs

SerDes Client Registers

Registerdescription Reg 1-63 see Lattice Handbook

0x40

SerDesPselReg

SerDesPreselect Register (8bit ) [Hw: syn, WAck1, RAck1]

Preselects the SerDes Quad and Channel. Control by SW or

JTag via Orcastra is determined.

TSIP Interface Test Pattern Generator Block (TstPatGenBlk) [Hw: Cy0]

The TstPatGen generates a pseudo random binary sequence with the aid of a 11-bit LFSR (feedback

taps on stage nine and eleven) and sends it to a Dsp via the TSIP interface or to the Tsip2Des block

substituting the original data. Alternatively a static pattern can be inserted. The substituted TSIP link

is selectable between 0 and 59. The TSIP timeslot is selectable between 0 and 511. Access via SPI-

bus from GlueFpga (occupies 256 Byte address area), hereof assigned to this block: 50...5F.

Address

Acronym

Description

0x50

TstPatGenLnkTsReg

Test Pattern Generator Link and Timeslot Register (16bit)

[Hw: asyn , WAck3, RAck3]

This registers selects timeslot TSIP-link for the test pattern

transmission of instead of payload data.

0x52

TstPatGenDatReg

Test Pattern Generator Data Register (8bit ) [Hw: asyn , WAck3

, RAck3]

This registers provides the test pattern to be transmitted in

the case of static pattern transmission.

Not used in the case of pseudo random pattern transmission.