4 tsip to serializer converter block (tsip2serblk), Table 8-184, Test pattern comparator error count register – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 393: Cpld and fpga

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

393

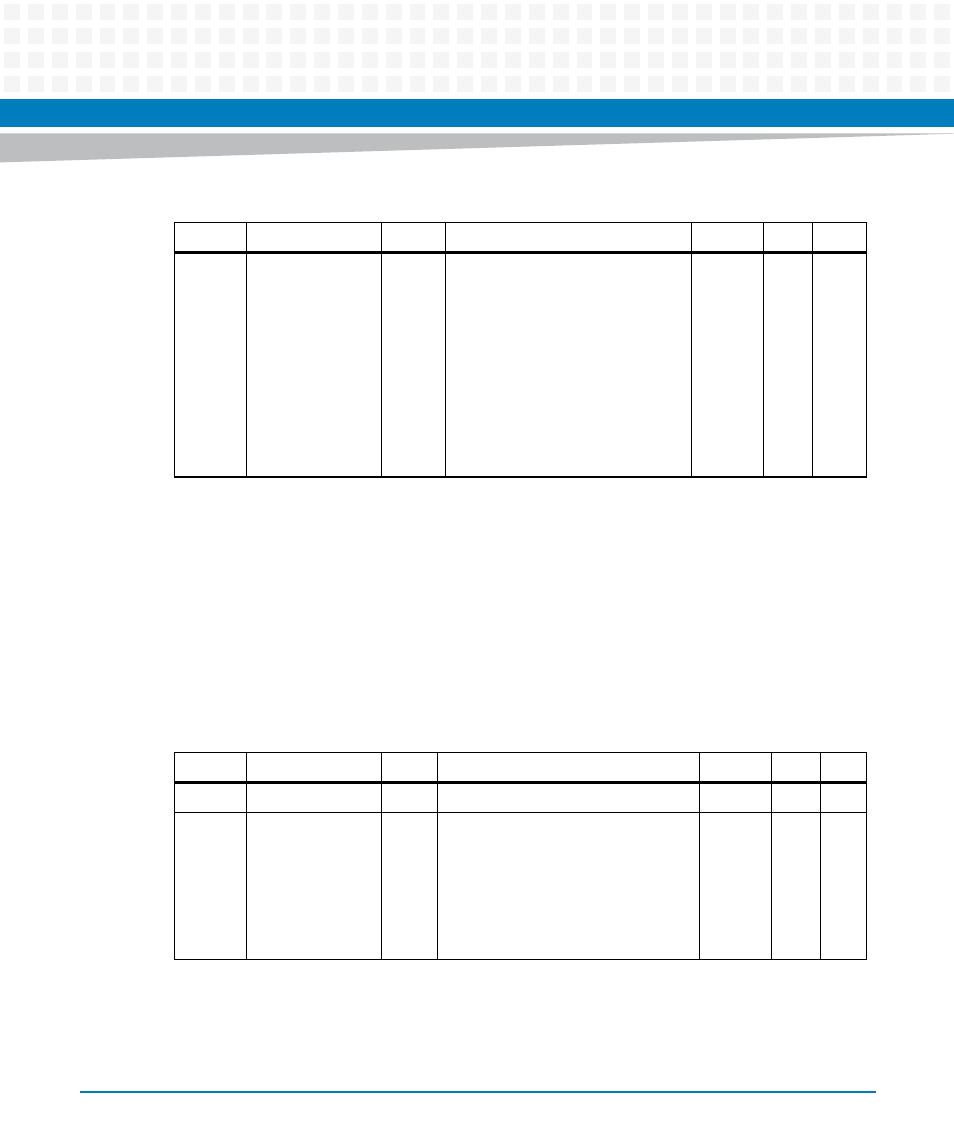

8.4.2.3.6 Test Pattern Comparator Error Count Register

Address: 0x6C, TstPatCmpErrorCntReg

Width: 32 bit

After synchronization of the static pattern or the PRBS receiver this registers counts bit errors.

The counter sticks at 0xFFFFFF. It is cleared, when TstPatCmpRxPatEn bit changes from 0 to 1.

i.e. the receiver is reenabled again.

8.4.2.4

TSIP to Serializer Converter Block (Tsip2SerBlk)

Resets:

23...0

TstPatCmpSyncC

nt

R

Time elapsed since measurement

has started after successful

synchronization (value x 125μs).

The counter sticks at 0xFFFFFF.

The count keeps its status after

the receiver is stopped, thus

showing its value during the last

measurement.The count is

cleared, when TstPatCmpRxPatEn

bit changes from 0 to 1. i.e. the

receiver is reenabled again.

0x0

F

F

Table 8-183 Test Pattern Synchronization Status Register (continued)

Bit

Acronym

Type

Description

Default

Pwr

Soft

Table 8-184 Test Pattern Comparator Error Count Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

29...24

-

-

reserved

undef

-

-

23...0

TstPatCmpErrCnt R

Bit error count. The count keeps its

status after the receiver is stopped,

thus showing its value during the

last measurement.The count

cleared, when TstPatCmpRxPatEn

bit changes from 0 to 1. i.e. the

receiver is reenabled again.

0x0

F

F