Table 8-175, Serdespreselect register, Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 386

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

386

Width: 8 bit

Preselects the SerDes Quad and Channel. Control by SW or JTag via Orcastra is determined.

8.4.2.2

TSIP Interface Test Pattern Generator Block (TstPatGenBlk)

Resets:

Pwr = Power On Reset

Soft = Soft Reset

The TstPatGen generates a pseudo random binary sequence with the aid of a 11-bit LFSR

(feedback taps on stage nine and eleven) and sends it to a Dsp via the TSIP interface or to the

Tsip2Des block substituting the original data. Alternatively a static pattern can be inserted. The

substituted TSIP link is selectable between 0 and 59.

The TSIP timeslot is selectable between 0 and 511.

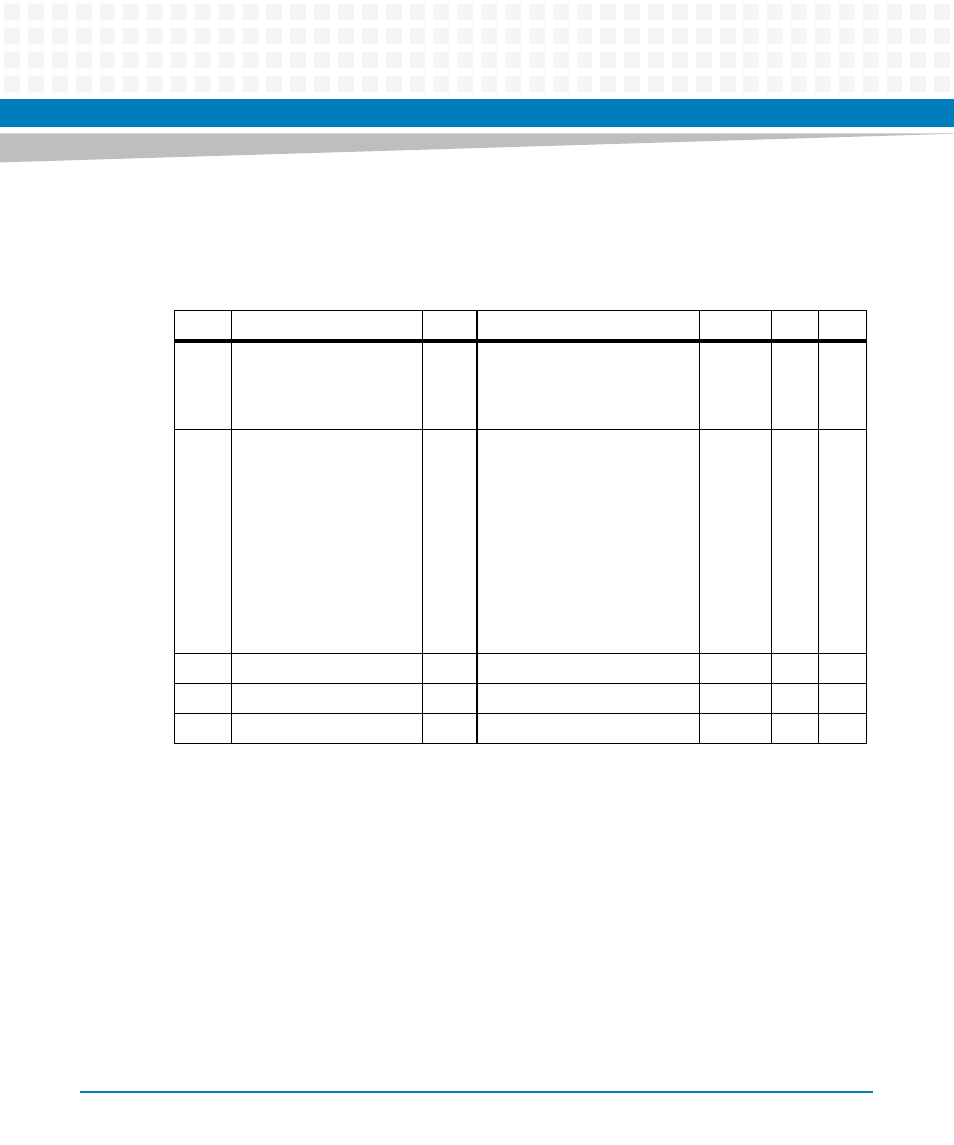

Table 8-175 SerDesPreselect Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

7

SerDesCltIfEn

RW

0b1: SerDesCltIfEn, Enables

access to Lattice Serdes client

interface for SW (disables

Orcastra access via JTAG)

0b0

X

X

6

SerDesCltConf2RegCopy

RW

0b0: SerDesCltConf2RegCopy,

when set, a value written to

any SerDes client register is

discarded, but all SerDes client

registers are initialized as

specified in the Fpga

configuration bitstream.

Values are copied from

background configuration

memory to SerDes client

registers.

0b0

X

X

5

-

-

reserved

undef

-

-

4...3

QuadAddr

RW

Quad Address

0b00

X

X

2...0

ChanAddr

RW

Channel Address

0b000

X

X