Table 8-211, Synchronization and error monitor reset register, Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 418: 3 synchronization and error monitor reset register

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

418

8.4.2.9.3 Synchronization and Error Monitor Reset Register

Address: 0xC2, SyncErrMonResReg

Width: 8 bit

The bits of this register reset the respective bits in SyncErrMonReg. Writing a 1 to a bit in

SyncErrMonResReg resets the corresponding bit in SyncErrMonReg. The error bit in

SyncErrMonReg is kept reset until writing a 0 to the corresponding bit in SyncErrMonResReg

reenables its monitor function again.

1

NoRefFrameSync

R

0b1: NoRefFrameSync, indication of

a lack or erroneous reference frame

synchronizations signal from the

Synchronous Equipment Timing

Source (Semtech ACS8520)

0b0

F

F

0

NoMainClkPllLock

R

0b1: NoMainClkPllLock, indication

that the main clock PLL is not locked

to 32.768 MHz reference clock from

the Synchronous Equipment Timing

Source (Semtech ACS8520)

0b0

F

Table 8-210 Synchronization and Error Monitor Register (continued)

Bit

Acronym

Type

Description

Default

Pwr

Soft

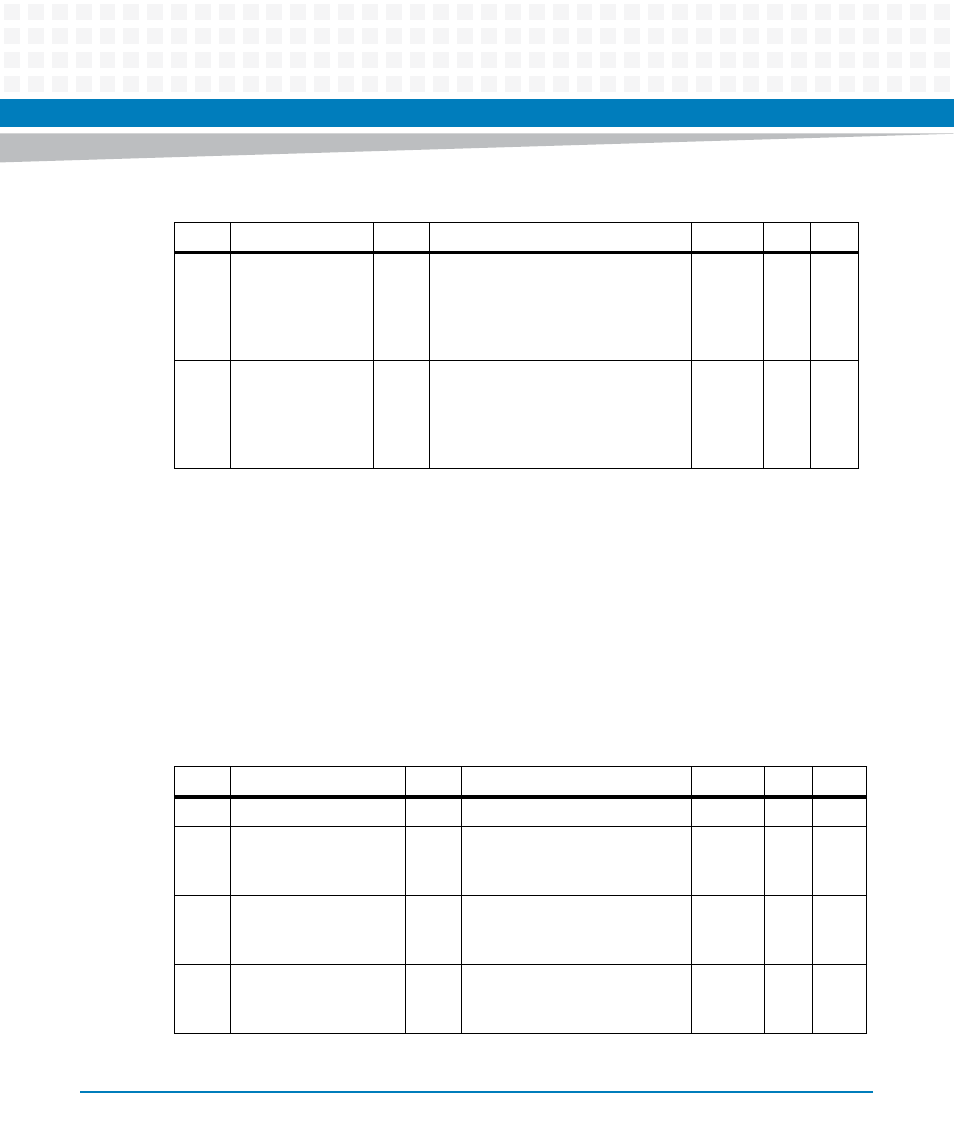

Table 8-211 Synchronization and Error Monitor Reset Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

7...5

-

-

reserved

undef

-

-

4

SciIntrptReset

RW

0b1: SciIntrptReset, resets the

client interfaces interrupt in

SyncErrMonReg

0b0

X

X

3

SerdesRcvErrorReset

RW

0b1: SerdesRcvErrorReset,

resets the SerdesRcvError in

SyncErrMonReg

0b0

X

X

2

SerdesTrmErrorReset

RW

0b1: SerdesTrmErrorReset,

resets the SerdesTrmError in

SyncErrMonReg

0b0

X

X