Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 391

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

391

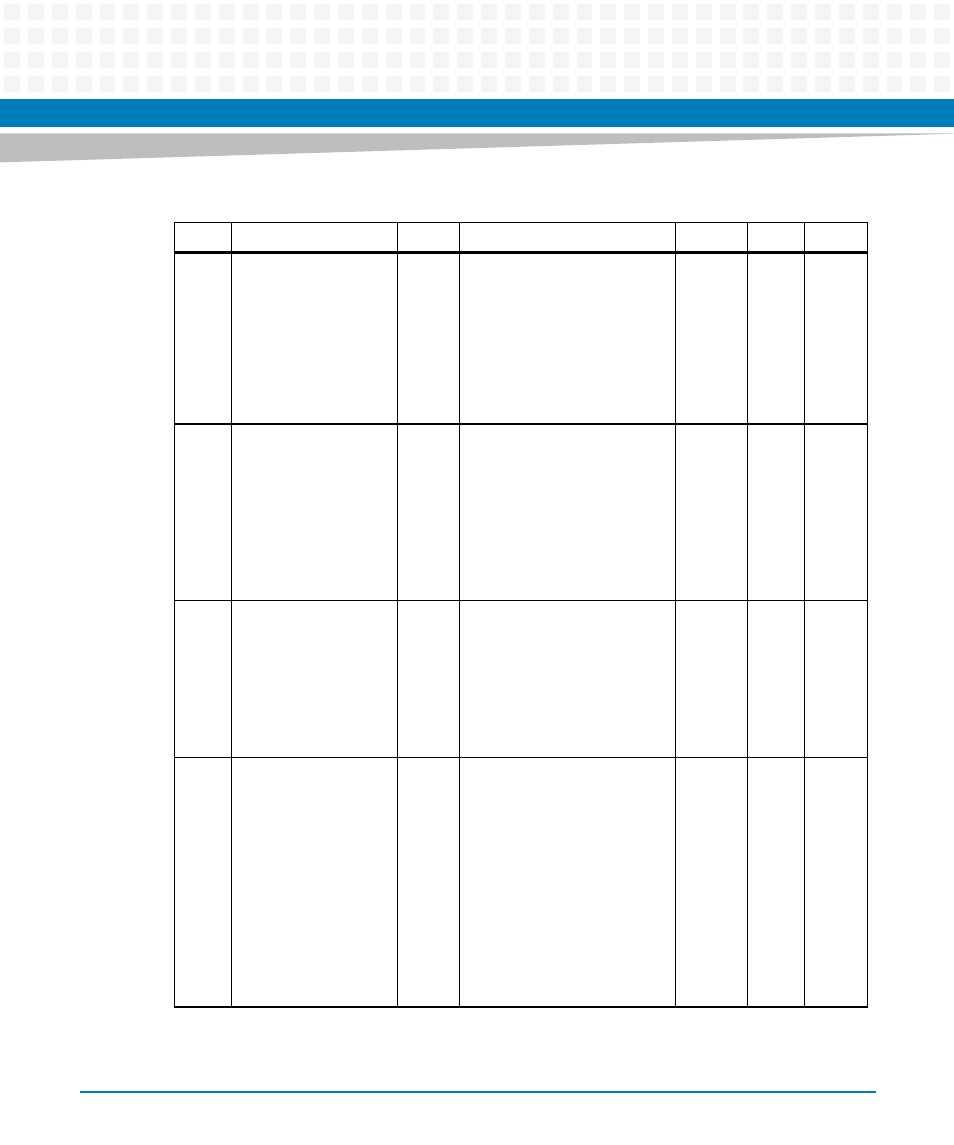

3

TstPatCmpBitstInvert

RW

0b1: TstPatCmpBitstrInvert,

selects that test pattern

bitstream is received inverted

0b0:

TstPatCmpBitstrNotInvert,

selects that test pattern

bitstream is received not

inverted

0b0

X

X

2

TstPatCmpSrcSel

RW

Specifies the pattern

destination:

0b1: TstPatOfDsp, selects

that test pattern are received

from Dsp

0b0: TstPatOfSer, selects that

test pattern are received from

Des2Tsip block

0b0

X

X

1

TstPatCmpPatSel

RW

Specifies the destination for

the pattern reception:

0b1: TstPatCmpPrbs, selects

the PRBS Comparator

0b0: TstPatCmpStatic,

selects the static pattern

receive register

0b0

X

X

0

TstPatCmpRxPatEn

RW

0b1: TstPatCmpRxPatEn,

enables the pattern

reception. Error and frame

counters and the

synchronization status bit are

cleared, when this bit

changes from 0 to 1.

A time of 125us delay has to

be taken into account, till the

comparator has stopped

after resetting

TstPatCmpRxPatEn bit.

0b0

X

X

Table 8-182 Test Pattern Comparator Control Register (continued)

Bit

Acronym

Type

Description

Default

Pwr

Soft