Table 8-76, Spp os reset source indication register, Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 303: 12 spp os ipmc watchdog timeout register

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

303

8.2.2.3.12 SPP OS IPMC Watchdog Timeout Register

When one of the IPMC Watchdog Timeout: bit of

Table "IPMC Watchdog Timeout Register" on

is set the corresponding BIOS IPMC Watchdog Timeout bit is set. The BIOS clears this

status bit, writing one.

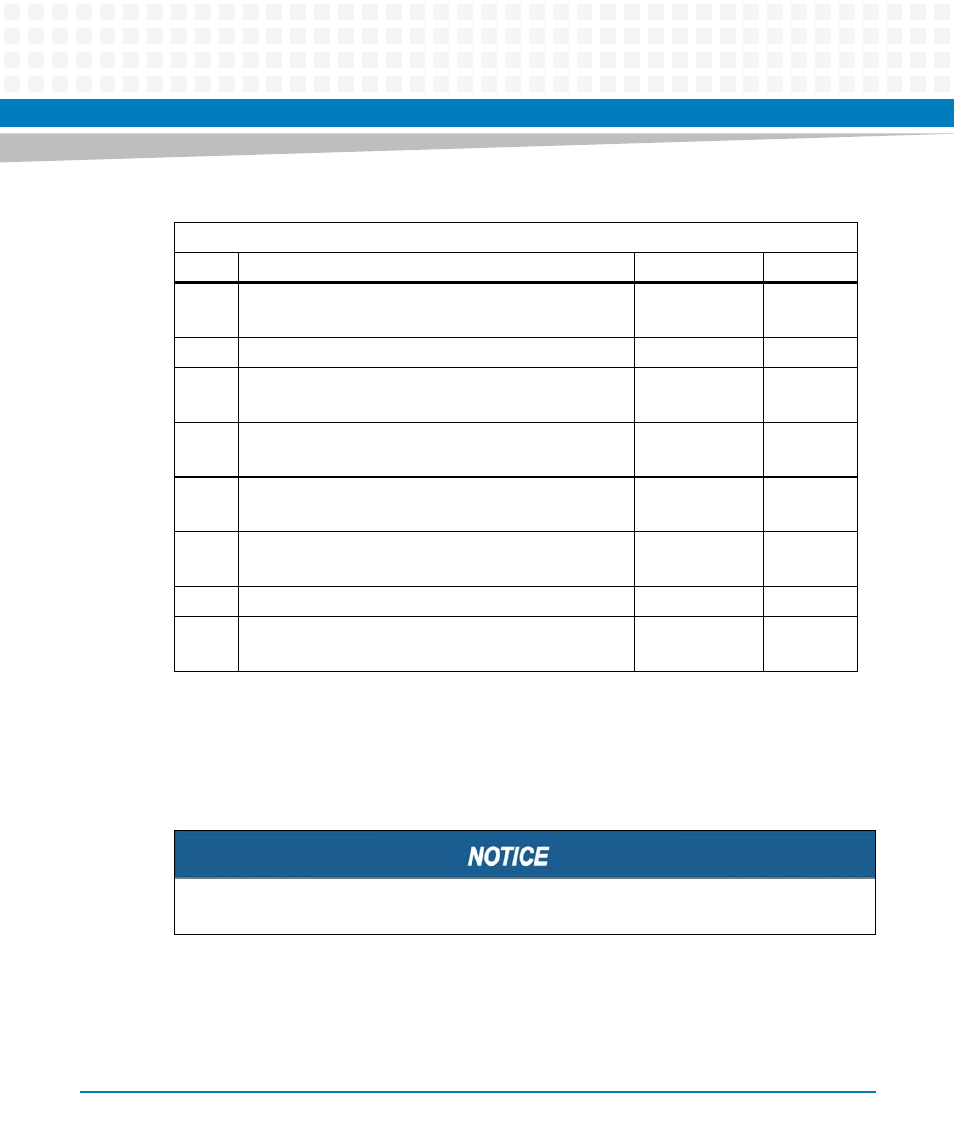

Table 8-76 SPP OS Reset Source Indication Register

Address: 0x0E

Bit

Description

Default

Access

0

PWR_GOOD Payload Power-on reset

1: Reset occurred

PWR_GOOD:1

SPP: r/w1c

IPMC: r

1

Reserved

0

r

2

PB_RST_ face plate push button reset

1: Reset occurred

PWR_GOOD:0

SPP: r/w1c

IPMC: r

3

SW Programmable Hardware Watchdog reset

1: Reset occurred

PWR_GOOD:0

SPP: r/w1c

IPMC: r

4

RTM_PB_RST_ Reset key at RTM

1: Reset occurred

PWR_GOOD:0

SPP: r/w1c

IPMC: r

5

SPP_HRESET_REQ_ signal from SPP

1: Reset occurred

PWR_GOOD:0

SPP: r/w1c

IPMC: r

6

Reserved

0

r

7

IPMC_RST_ REQ_ Payload Reset from IPMC.

1: Reset occurred

PWR_GOOD:0

SPP: r/w1c

IPMC: r

BIOS should never write to this register.