Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 381

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

381

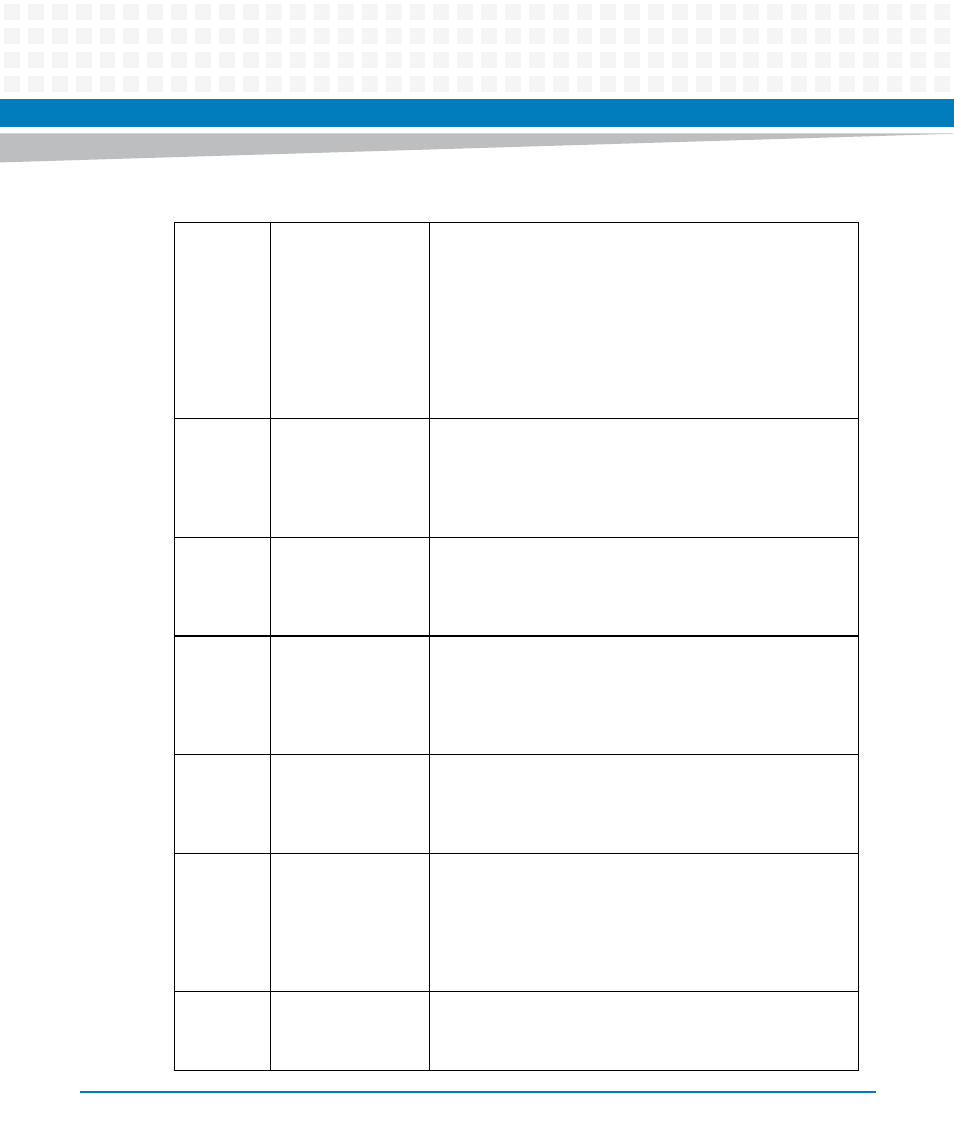

0xC2

SyncErrMonResReg

Synchronization and Error Monitor Reset Register (8bit) [Hw:

syn, WAck1, RAck1]

The bits of this register reset the respective bits in

SyncErrMonReg. Writing a 1 to a bit in SyncErrMonResReg

resets the corresponding bit in SyncErrMonReg. The error bit

in SyncErrMonReg is kept reset until writing a 0 to the

corresponding bit in SyncErrMonResReg reenables its

monitor function.again.

0xC3

SyncErrMonMaskRe

g

Synchronisation and Error Monitor Mask Register (8bit) [Hw:

syn, WAck1, RAck1]

The bits of this register mask the bits of the SyncErrMonReg

for the generation of the Host Event Interrupt (HOUT).

0xC4

DebugLedReg

Debug LED Register (8bit) [Hw: syn, WAck1, RAck1]

This register controls the condition of the lower 3 LEDs for

Debug purposes

0xC5

BaseIdReg

Base Board and Module Place Identifier (8bit ) [Hw: syn ,

WAck1, RAck1]

This register shows the status of the base board module place

identifier pins

0xC6

ModuleFunctionalId

Reg

Module Functional Identifier (8bit ) [Hw: syn , WAck1 , RAck1]

This register shows the functional environment version, e.g

board rev

0xC7

CompResReg

Component Reset Register (8bit ) [Hw: syn , WAck1 , RAck1]

The bits of this register reset the respective components, e.g.

Sedes Quad. Writing a 1 to a bit puts the respective

component into reset, until writing a 0 reenables its function

again.

0xC8

FpgaVersionReg

Dsp Fpga Version Register (32bit ) [Hw: syn , WAck1 , RAck1]

This register shows the version of the DspFpga

Table 8-174 Logic DSP FPGA Register Overview (continued)