Table 8-212, Synchronisation and error monitor mask register, Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 419: 4 synchronisation and error monitor mask register

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

419

8.4.2.9.4 Synchronisation and Error Monitor Mask Register

Address: 0xC3, SyncErrMonMaskReg

Width: 8 bit

The bits of this register mask the bits of the SyncErrMonReg for the generation of the Host

Event Interrupt (HOUT).

1

NoRefFrameSyncReset

RW

0b1: NoRefFrameSyncReset,

resets NoRefFrameSync

indication bit in

SyncErrMonReg

0b0

X

X

0

NoMainClkPllLockRese

t

RW

0b1: NoMainClkPllLockReset,

resets NoMainClkPllLock

indication bit in

SyncErrMonReg

0b0

X

X

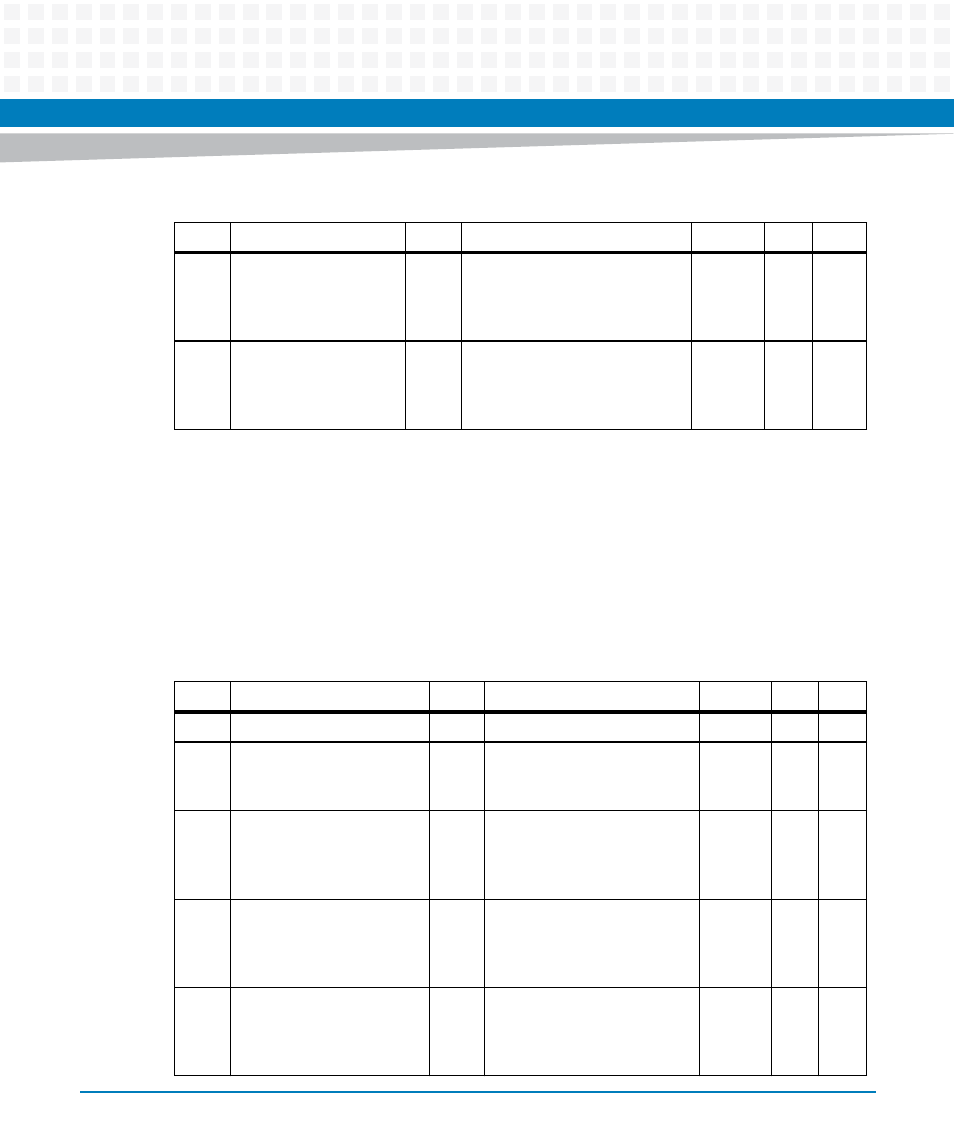

Table 8-211 Synchronization and Error Monitor Reset Register (continued)

Bit

Acronym

Type

Description

Default

Pwr

Soft

Table 8-212 Synchronisation and Error Monitor Mask Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

7...5

-

-

reserved

undef

-

-

4

SciIntrptMask

RW

0b1: SciIntrptEnable, enables

the client interfaces interrupt

generation

0b0

X

X

3

SerdesRcvErrorIntrptMask

RW

0b1:

SerdesRcvErrorIntrptEnable,

enables the SerdesRcvError

interrupt generation

0b0

X

X

2

SerdesTrmErrorIntrptMask

RW

0b1:

SerdesTrmErrorIntrptEnable,

enables the SerdesTrmError

interrupt generation

0b0

X

X

1

NoRefFrameSyncIntrptMa

sk

RW

0b1:

NoRefFrameSyncIntrptEnabl

e, enabless NoRefFrameSync

interrupt generation

0b0

X

X