Table 8-52, Interrupt enable register (ier), if dlab=0, Table 8-53 – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 278: Uart interrupt priorities2, Cpld and fpga

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

278

This register enables four types of interrupts which independently activate the int signal and

set a value in the Interrupt Identification Register. Each of the four interrupt types can be

disabled by resetting the appropriate bit of the IER register. Similarly, by setting the

appropriate bits, selected interrupts can be enabled.

- Interrupt Identification Register (IIIR)

In order to minimize software overhead during data character transfers, the UART prioritizes

interrupts into four levels (listed in

) and records these in the Interrupt Identification

Register. The Interrupt Identification Register (IIR) stores information indicating that a

prioritized interrupt is pending and the source of that interrupt.

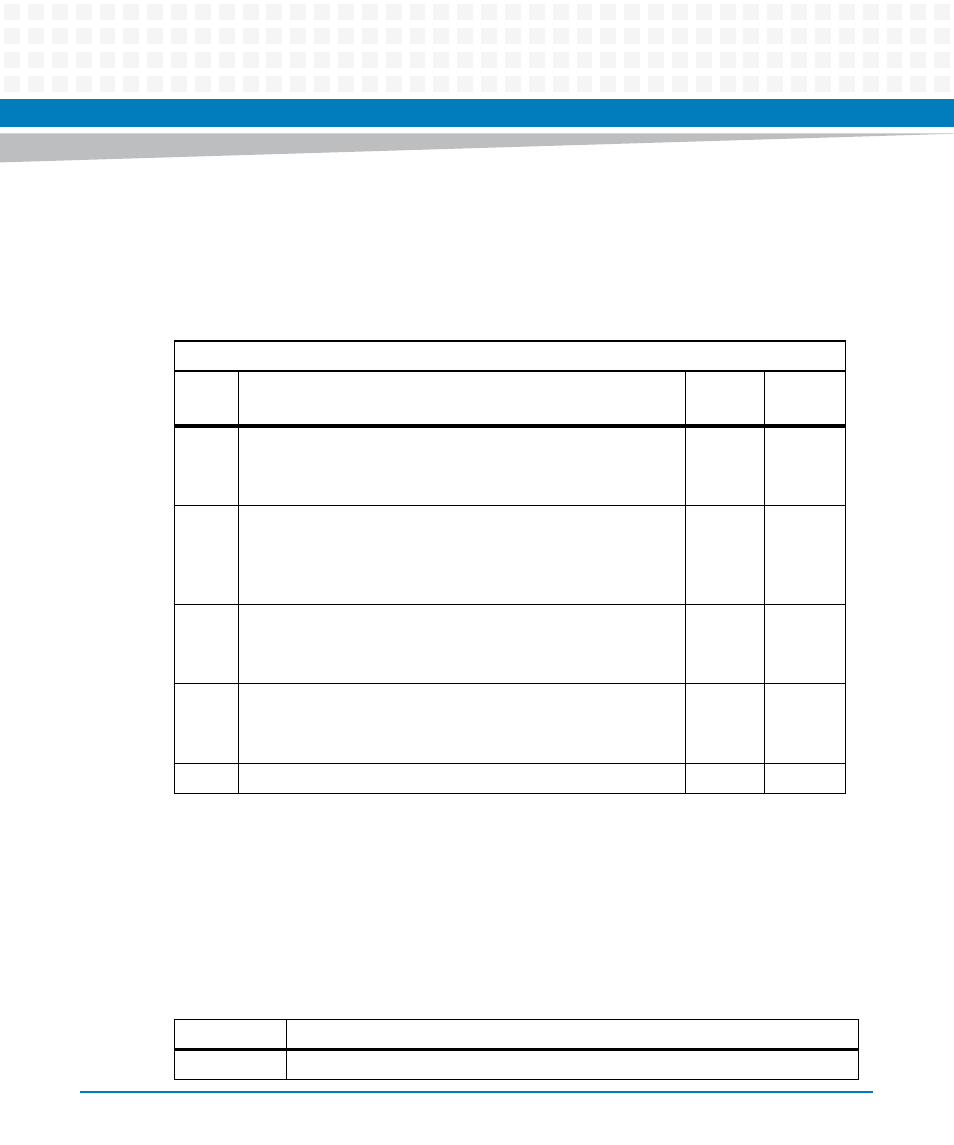

Table 8-52 Interrupt Enable Register (IER), if DLAB=0

IO Address: Base + 1

Bit

Description

Default

Access

0

Receive data interrupt enable/disable:

1: receive data interrupt enabled

0: receive data interrupt disabled

0

GPP: r/w

1

Transmitter holding register empty (THRE) interrupt

enable/disable

1: THRE interrupt enabled

0: THRE interrupt disabled

0

GPP: r/w

2

Receiver line status interrupt enable/disable

1: receiver line status interrupt enabled

0: receiver line status interrupt disabled

0

GPP: r/w

3

Modem status interrupt enable/disable:

1: modem status interrupt enabled

0: modem status interrupt disabled

0

GPP: r/w

7:4

Reserved

0

r

Table 8-53 UART Interrupt Priorities2

Priority Level

Interrupt Source

1 (highest)

Receiver Line Status. One or more error bits were set.