Table 8-183, Test pattern synchronization status register, Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 392: 5 test pattern synchronization status register

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

392

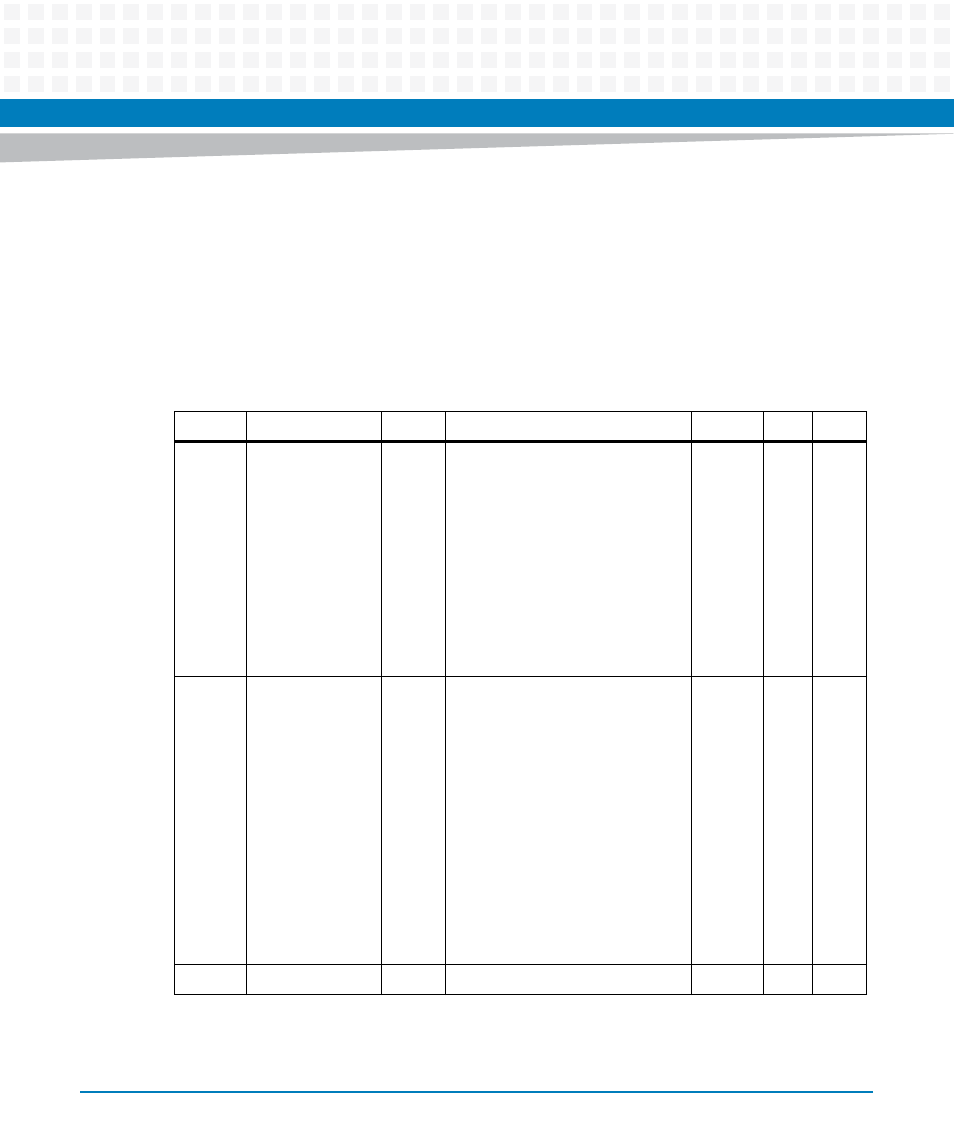

8.4.2.3.5 Test Pattern Synchronization Status Register

Address: 0x68, TstPatCmpSyncStaReg

Width: 32 bit

This registers indicates the synchronization status of the received static pattern or the PRBS bit

stream.

Table 8-183 Test Pattern Synchronization Status Register

Bit

Acronym

Type

Description

Default

Pwr

Soft

31

TstPatCmpSync

R

0b1: TstPatCmpSync, indicates

that the specified receiver is

synchronized to the specified

static pattern or the PRBS bit

stream.

The bit shows the current

synchronization status "live". It is

only valid when the receiver is

running, i.e. TstPatCmpRxPatEn is

set.

0b0

F

F

30

TstPatCmpSyncL

ost

R

0b1: TstPatCmpSyncLost,

indicates that the specified

receiver has lost synchronization

after a first successful

synchronization to the specified

static pattern or the PRBS bit

stream.

The bit keeps its status after the

receiver is stopped, thus showing

its value during the last

measurement. It is cleared, when

TstPatCmpRxPatEn bit changes

from 0 to 1. i.e. the receiver is

reenabled again.

0b0

F

F

29...24

-

-

reserved

undef

-

-