Table 8-16, Power-up failure codes part 5 register, Table 8-17 – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 254: Power-up failure codes part 6 register, Cpld and fpga

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

254

6

GPP Thermal Trip from Arrendale. Last inverted Level GPP_THERMTRIP_.

Triggers IPMC H8S_CPLD_IRQ_ interrupt

0

SPI: r

7

Glue FPGA Configuration Error from SED. Last level CONF_CRC_ERR.

Triggers IPMC H8S_CPLD_IRQ_ interrupt

0

SPI: r

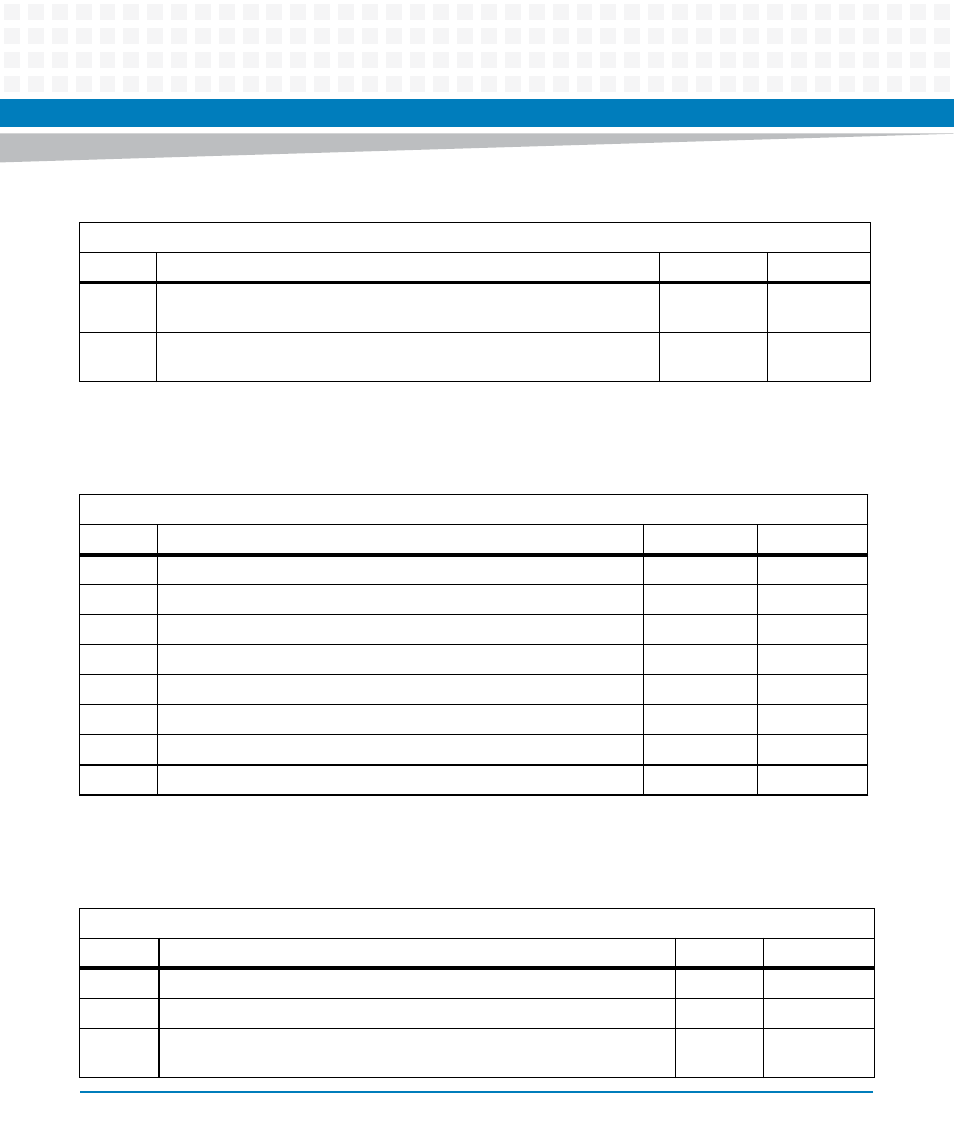

Table 8-15 Power-up Failure Codes Part 4 Register (continued)

CPLD Address: 0x0B

Bit Description

Default

Access

Table 8-16 Power-up Failure Codes Part 5 Register

CPLD Address: 0x0C

Bit Description

Default

Access

0

FPGA DONE Glue. Last inverted level FPGA_DONE

0

SPI: r

1

FPGA INIT_N Glue. Last inverted level FPGA_INIT_

0

SPI: r

2

FPGA DONE DMC Base. Last inverted level DMC_FPGA_DONE

0

SPI: r

3

FPGA INIT_N DMC Base. Last inverted level DMC_FPGA_INIT_

0

SPI: r

4

FPGA DONE DMC 1. Last inverted level DMC1_FPGA_DONE

0

SPI: r

5

FPGA INIT_N DMC 1. Last inverted level DMC1_FPGA_INIT_

0

SPI: r

6

FPGA DONE DMC 2. Last inverted level DMC1_FPGA_DONE

0

SPI: r

7

FPGA INIT_N DMC 2. Last inverted level DMC2_FPGA_INIT_

0

SPI: r

Table 8-17 Power-up Failure Codes Part 6 Register

CPLD Address: 0x0D

Bit Description

Default

Access

0

FPGA DONE ARTM. Last inverted level RTM_FPGA_DONE

0

SPI: r

1

FPGA INIT_N ARTM. Last inverted level RTM_FPGA_INIT_

0

SPI: r

2

CLK_EN_N from IMVP Core Power GPP. Last inverted Level

PWRGD_CK_GPP

0

SPI: r