Cpld and fpga – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 382

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

382

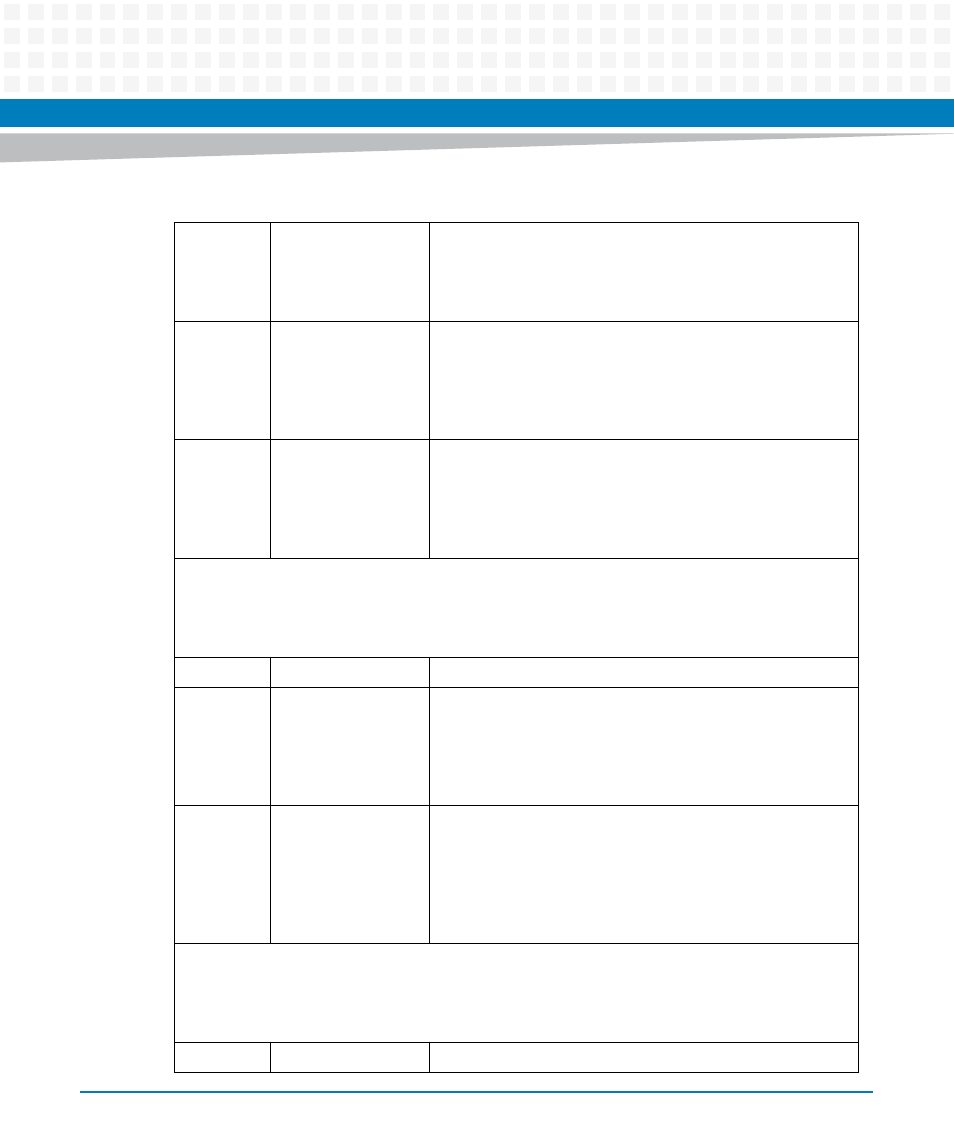

0xCC

UnOccpdAddrMonR

eg

Unoccupied Address Access Monitor Register (8bit ) [Hw: syn

, WAck1 , RAck1]

This register monitors the access to unoccupied address areas

0xCD

UnOccpdAddrMonR

esetReg

Unoccupied Address Access Monitor Reset Register (8bit )

[Hw: syn , WAck1 , RAck1]

This register resets the access to unoccupied address area

monitor and unoccupied address area address registers

0xD0

UnOccpdAddrMonA

ddrReg

Unoccupied Address Access Monitor Address Register (32bit )

[Hw: syn , WAck1 , RAck1]

This register stores the address of the last the access to

unoccupied an address area

Configuration Prom Update Registers (CfgPrmUpd) [Hw: Cy0]

Allows updating the serial configuration prom of the FPGA

Access via SPI- bus from GlueFpga (occupies 256 Byte address area) bridged to SPI bus to Config

Prom, hereof assigned to this block: D8...DF

Address

Acronym

Description

0xD8

CfgPrmUpdCtrReg

Configuration Prom Update Control Register (8bit ) [Hw: syn ,

WAck5 , RAck5 , WRP ]

Controls the update of the FPGA serial configuration prom by

the host processor via SPI bus.

0xD9

CfgPrmUpdDatReg

Configuration Prom Update Data Register (8bit ) [Hw: syn ,

WAck25, RAck25, WRP]

Holds the write data to sent to the FPGA serial configuration

prom when written and the read data received from the FPGA

serial configuration prom when read.

General Test Registers (GenTestRegs) [Hw: Cy0]

General Test Registers

Access via SPI- bus from GlueFpga (occupies 256 Byte address area), hereof assigned to this block:

E0...EF

Address

Acronym

Description

Table 8-174 Logic DSP FPGA Register Overview (continued)