NEC Network Controller uPD98502 User Manual

Page 82

CHAPTER 2 V

R

4120A

82

Preliminary User’s Manual S15543EJ1V0UM

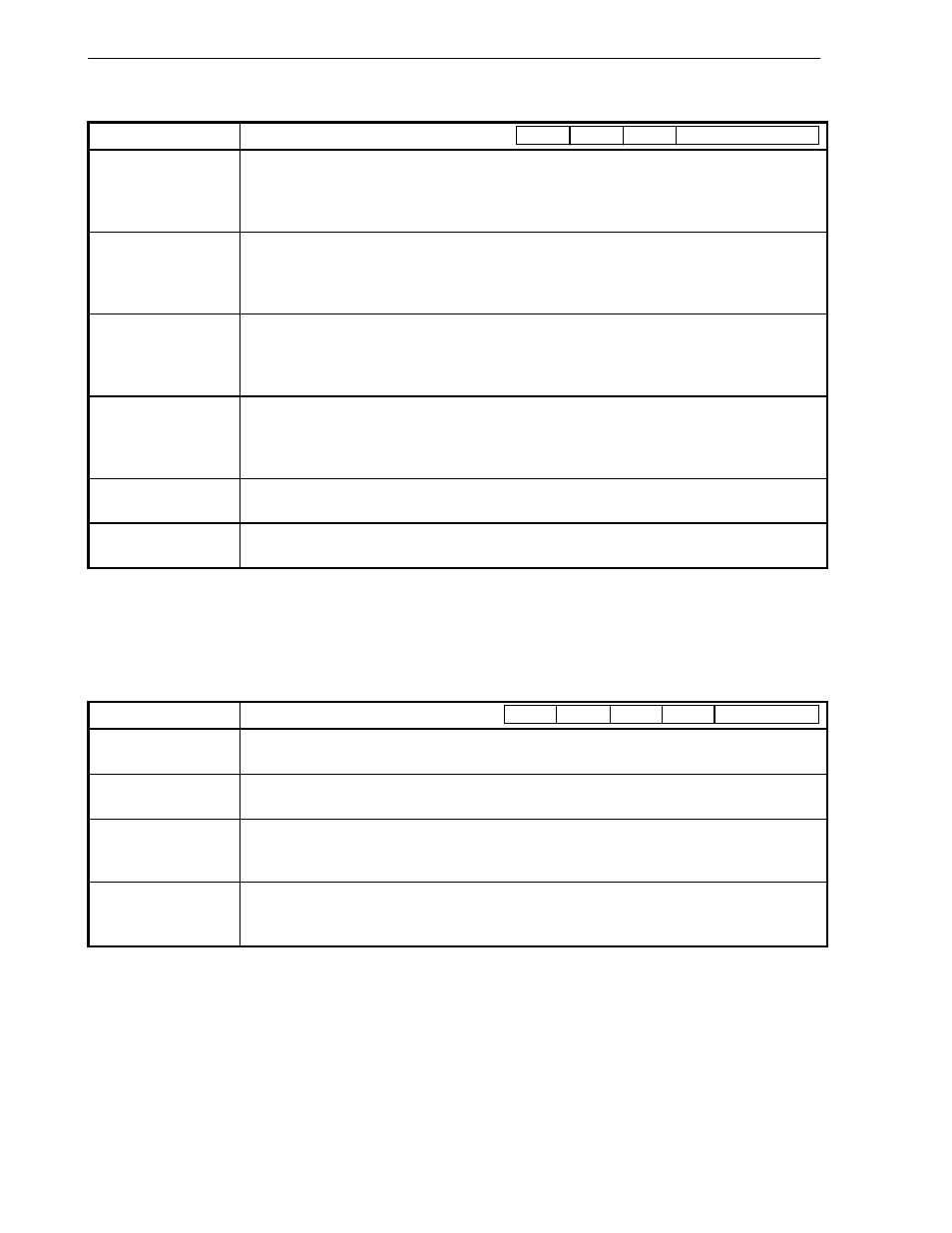

Table 2-20. Special Instructions (Extended ISA) (2/2)

Instruction

Format and Description

Trap If Greater Than Or

Equal Immediate

TGEI rs, immediate

The contents of register rs are compared with 16-bit sign-extended immediate data, treating both

operands as signed integers. If the contents of register rs are greater than or equal to 16-bit sign-

extended immediate data, an exception occurs.

Trap If Greater Than Or

Equal Immediate

Unsigned

TGEIU rs, immediate

The contents of register rs are compared with 16-bit zero-extended immediate data, treating both

operands as unsigned integers. If the contents of register rs are greater than or equal to 16-bit sign-

extended immediate data, an exception occurs.

Trap If Less Than

Immediate

TLTI rs, immediate

The contents of register rs are compared with 16-bit sign-extended immediate data, treating both

operands as signed integers. If the contents of register rs are less than 16-bit sign-extended

immediate data, an exception occurs.

Trap If Less Than

Immediate Unsigned

TLTIU rs, immediate

The contents of register rs are compared with 16-bit zero-extended immediate data, treating both

operands as unsigned integers. If the contents of register rs are less than 16-bit sign-extended

immediate data, an exception occurs.

Trap If Equal

Immediate

TEQI rs, immediate

If the contents of register rs and immediate data are equal, an exception occurs.

Trap If Not Equal

Immediate

TNEI rs, immediate

If the contents of register rs and immediate data are not equal, an exception occurs.

2.2.2.5 System control coprocessor (CP0) instructions

System control coprocessor (CP0) instructions perform operations specifically on the CP0 registers to manipulate

the memory management and exception handling facilities of the processor.

Table 2-21. System Control Coprocessor (CP0) Instructions (1/2)

Instruction

Format and Description

Move To System

Control Coprocessor

MTC0 rt, rd

The word data of general register rt in the CPU are loaded into general register rd in the CP0.

Move From System

Control Coprocessor

MFC0 rt, rd

The word data of general register rd in the CP0 are loaded into general register rt in the CPU.

Doubleword Move To

System Control

Coprocessor 0

DMTC0 rt, rd

The doubleword data of general register rt in the CPU are loaded into general register rd in the CP0.

Doubleword Move

From System Control

Coprocessor 0

DMFC0 rt, rd

The doubleword data of general register rd in the CP0 are loaded into general register rt in the CPU.

REGIMM

immediate

rs

sub

COP0

sub

rt

0

rd