Cache, Cache (1/4) – NEC Network Controller uPD98502 User Manual

Page 465

APPENDIX A MIPS III INSTRUCTION SET DETAILS

Preliminary User’s Manual S15543EJ1V0UM

465

CACHE

Cache (1/4)

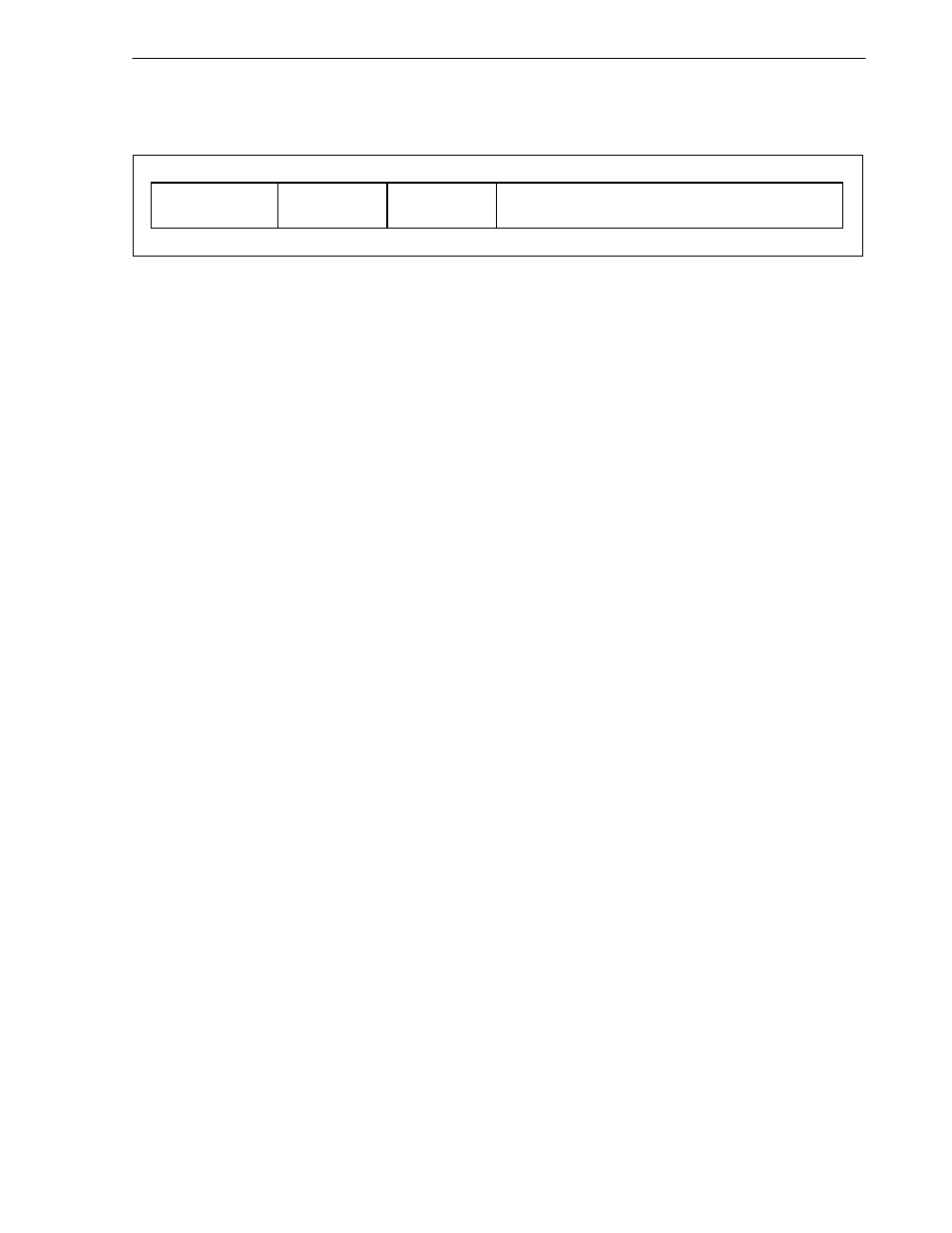

CACHE

base

CACHE

1 0 1 1 1 1

op

offset

31

26 25

21 20

16 15

0

6

5

5

16

Format:

CACHE op, offset (base)

Description:

The 16-bit

offset is sign-extended and added to the contents of general register base to form a virtual address.

The virtual address is translated to a physical address using the TLB, and the 5-bit sub-opcode specifies a cache

operation for that address.

If CP0 is not usable (User or Supervisor mode) and the CP0 enable bit in the Status register is clear, a coprocessor

unusable exception is taken. The operation of this instruction on any operation/cache combination not listed below,

or on a secondary cache that is not incorporated in V

R

4120A CPU, is undefined. The operation of this instruction

on uncached addresses is also undefined.

The Index operation uses part of the virtual address to specify a cache block.

For a primary cache of 2

CACHEBITS

bytes with 2

LINEBITS

bytes per tag, vAddrCACHEBITS...LINEBITS specifies the block.

Index_Load_Tag also uses vAddrLINEBITS...3 to select the doubleword for reading parity. When the

CE bit of the

Status register is set, Fill Cache op uses the PErr register to store parity values into the cache.

The Hit operation accesses the specified cache as normal data references, and performs the specified operation if

the cache block contains valid data with the specified physical address (a hit). If the cache block is invalid or

contains a different address (a miss), no operation is performed.