NEC Network Controller uPD98502 User Manual

Page 315

CHAPTER 6 USB CONTROLLER

Preliminary User’s Manual S15543EJ1V0UM

315

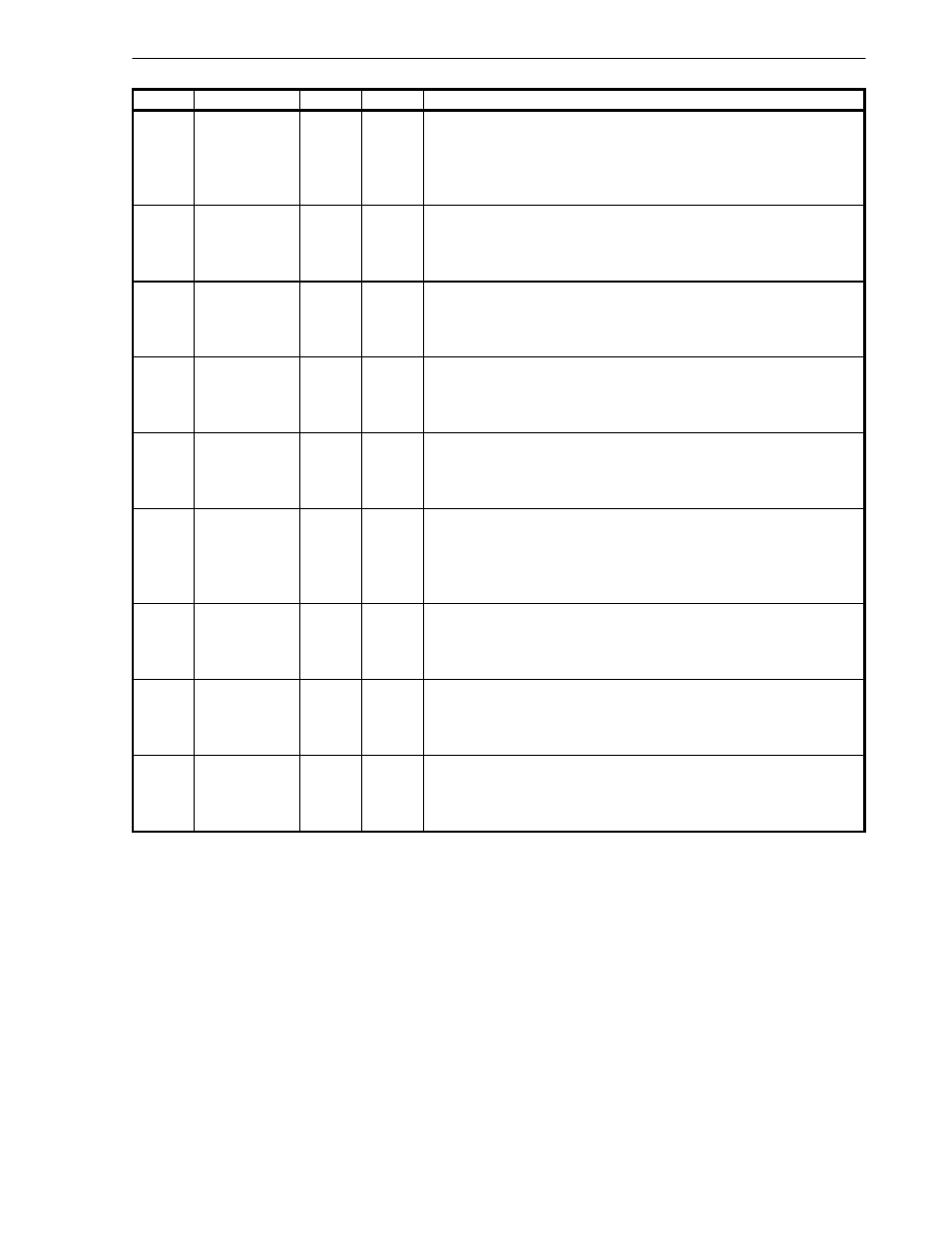

Bits

Field

R/W

Default

Description

8

EP1FU

RC

0

EP1 FIFO Error:

Bit that indicates that an underrun has occurred for the FIFO of EndPoint1

(Isochronous IN). When the FIFO empties while EndPoint1 is performing a

transaction, this bit is set to a ‘1’.

This bit is reset to a ‘0’ when the V

R

4120A reads this register.

7

EP6RF

RC

0

EP6 Rx Finished:

Bit that indicates that EndPoint6 (Interrupt OUT) has completed the receiving

of a data segment and issued the Rx Indication.

This bit is reset to a ‘0’ when the V

R

4120A reads this register.

6

EP5TF

RC

0

EP5 Tx Finished:

Bit that indicates that EndPoint5 (Interrupt IN) has completed the transmitting

of a data segment and issued the Tx Indication.

This bit is reset to a ‘0’ when the V

R

4120A reads this register.

5

EP4RF

RC

0

EP4 Rx Finished:

Bit that indicates that EndPoint4 (Bulk OUT) has completed the receiving of a

data segment and issued the Rx Indication.

This bit is reset to a ‘0’ when the V

R

4120A reads this register.

4

EP3TF

RC

0

EP3 Tx Finished:

Bit that indicates that EndPoint3 (Bulk IN) has completed the transmitting of a

data segment and issued the Tx Indication.

This bit is reset to a ‘0’ when the V

R

4120A reads this register.

3

EP2RF

RC

0

EP2 Rx Finished:

Bit that indicates that EndPoint2 (Isochronous OUT) has completed the

receiving of a data segment and issued the Rx Indication.

The timing when this bit will be set varies with Rx Mode.

This bit is reset to a ‘0’ when the V

R

4120A reads this register.

2

EP1TF

RC

0

EP1 Tx Finished:

Bit that indicates that EndPoint1 (Isochronous IN) has completed the

transmitting of a data segment and issued the Tx Indication.

This bit is reset to a ‘0’ when the V

R

4120A reads this register.

1

EP0RF

RC

0

EP0 Rx Finished:

Bit that indicates that EndPoint0 (Control) has completed the receiving of a

data segment and issued the Rx Indication.

This bit is reset to a ‘0’ when the V

R

4120A reads this register.

0

EP0TF

RC

0

EP0 Tx Finished:

Bit that indicates that EndPoint0 (Control) has completed the transmitting of a

data segment and issued the Tx Indication.

This bit is reset to a ‘0’ when the V

R

4120A reads this register.