NEC Network Controller uPD98502 User Manual

Page 113

CHAPTER 2 V

R

4120A

Preliminary User’s Manual S15543EJ1V0UM

113

(5) kseg3 (32-bit kernel mode, kernel space 3)

When KX = 0 in the Status register and the most-significant three bits of the virtual address space are 111, the

kseg3 virtual address space is selected; it is the current 512-Mbyte (2

29

-byte) kernel virtual space. The virtual

address is extended with the contents of the 8-bit ASID field to form a unique virtual address.

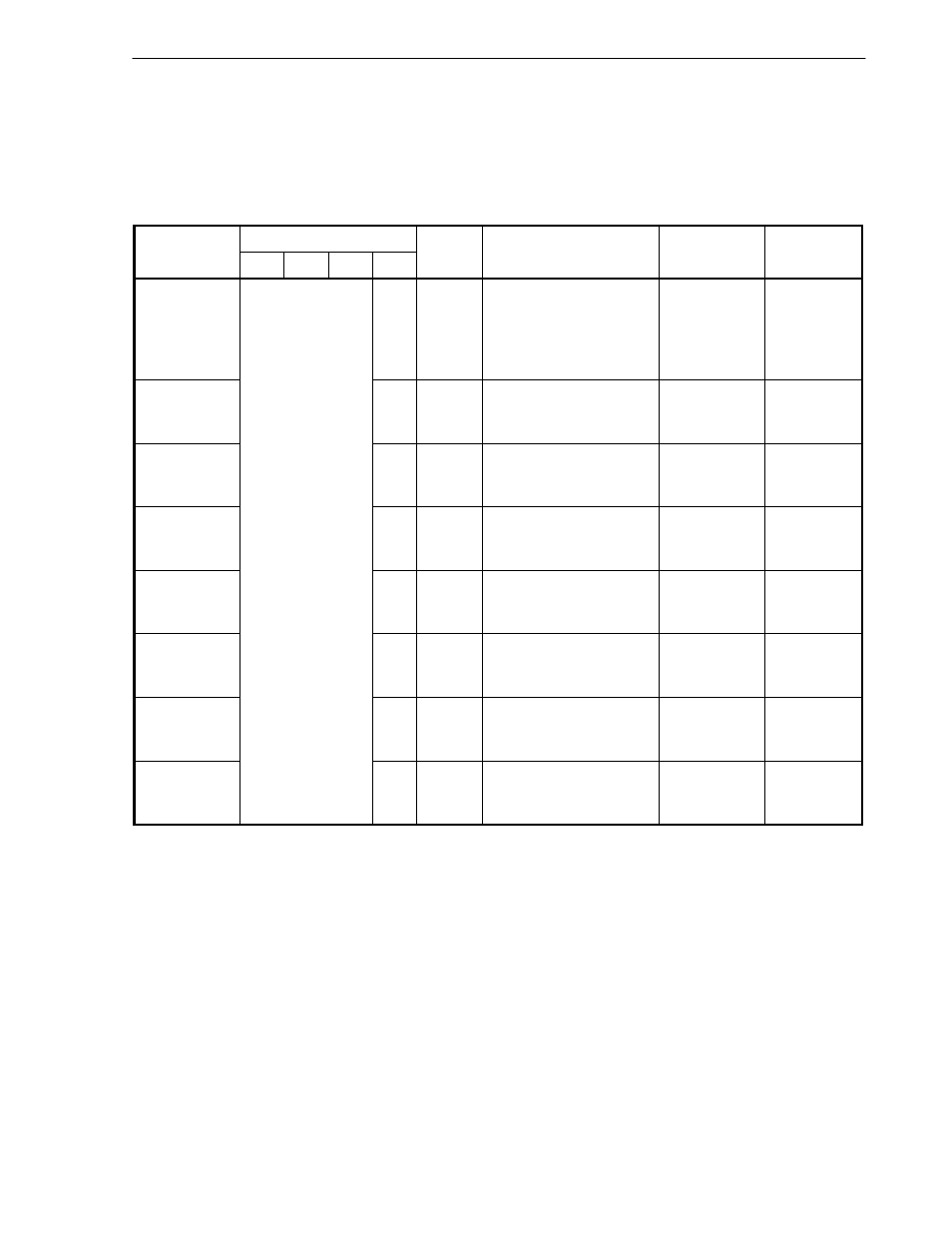

Table 2-30. 64-bit Kernel Mode Segments

Address Bit

Status Register Bit Value

Segment

Virtual Address

Physical

Size

Value

KSU

EXL

ERL

KX

Name

Address

A(63:62) = 00

KSU = 00

or

EXL = 1

or

ERL = 1

1

xkuseg

0000_0000_0000_0000H

to

0000_00FF_FFFF_FFFFH

TLB map

1 Tbyte

(2

40

bytes)

A(63:62) = 01

1

xksseg

4000_0000_0000_0000H

to

4000_00FF_FFFF_FFFFH

TLB map

1 Tbyte

(2

40

bytes)

A(63:62) = 10

1

xkphys

8000_0000_0000_0000H

to

BFFF_FFFF_FFFF_FFFFH

0000_0000H

to

FFFF_FFFFH

4 Gbytes

(2

32

bytes)

A(63:62) = 11

1

xkseg

C000_0000_0000_0000H

to

C000_00FF_7FFF_FFFFH

TLB map

2

40

to 2

31

bytes

A(63:62) = 11

A(63:31) = -1

1

ckseg0

FFFF_FFFF_8000_0000H

to

FFFF_FFFF_9FFF_FFFFH

0000_0000H

to

1FFF_FFFFH

512 Mbytes

(2

29

bytes)

A(63:62) = 11

A(63:31) = -1

1

ckseg1

FFFF_FFFF_A000_0000H

to

FFFF_FFFF_BFFF_FFFFH

0000_0000H

to

1FFF_FFFFH

512 Mbytes

(2

29

bytes)

A(63:62) = 11

A(63:31) = -1

1

cksseg

FFFF_FFFF_C000_0000H

to

FFFF_FFFF_DFFF_FFFFH

TLB map

512 Mbytes

(2

29

bytes)

A(63:62) = 11

A(63:31) = -1

1

ckseg3

FFFF_FFFF_E000_0000H

to

FFFF_FFFF_FFFF_FFFFH

TLB map

512 Mbytes

(2

29

bytes)

(6) xkuseg (64-bit kernel mode, user space)

When KX = 1 in the Status register and bits 63 and 62 of the virtual address space are 00, the xkuseg virtual

address space is selected; it is the 1-Tbyte (2

40

bytes) current user address space. The virtual address is

extended with the contents of the 8-bit ASID field to form a unique virtual address.

If the ERL bit of the Status register is 1, the user address space is assigned 2 Gbytes (2

31

bytes) without TLB

mapping and becomes unmapped (with virtual addresses being used as physical addresses) and uncached so

that the cache error handler can use it. This allows the Cache Error exception code to operate uncached using r0

as a base register.