4 mailbox – NEC Network Controller uPD98502 User Manual

Page 276

CHAPTER 4 ATM CELL PROCESSOR

276

Preliminary User’s Manual S15543EJ1V0UM

4.8.4 Mailbox

ATM Cell Processor uses mailboxes as ring buffers in system memory. The structure of a mailbox and the defined

addresses are as follows.

Mailbox start address (A_MSA[3:0])

:The start address of the mailbox

Mailbox bottom address (A_MBA[3:0])

:The bottom address of the mailbox (address following the last address)

Mailbox write address (A_MWA[3:0])

:The write pointer

Mailbox tail address (A_MTA[3:0])

:The tail address that has been read by the host and which is to be updated

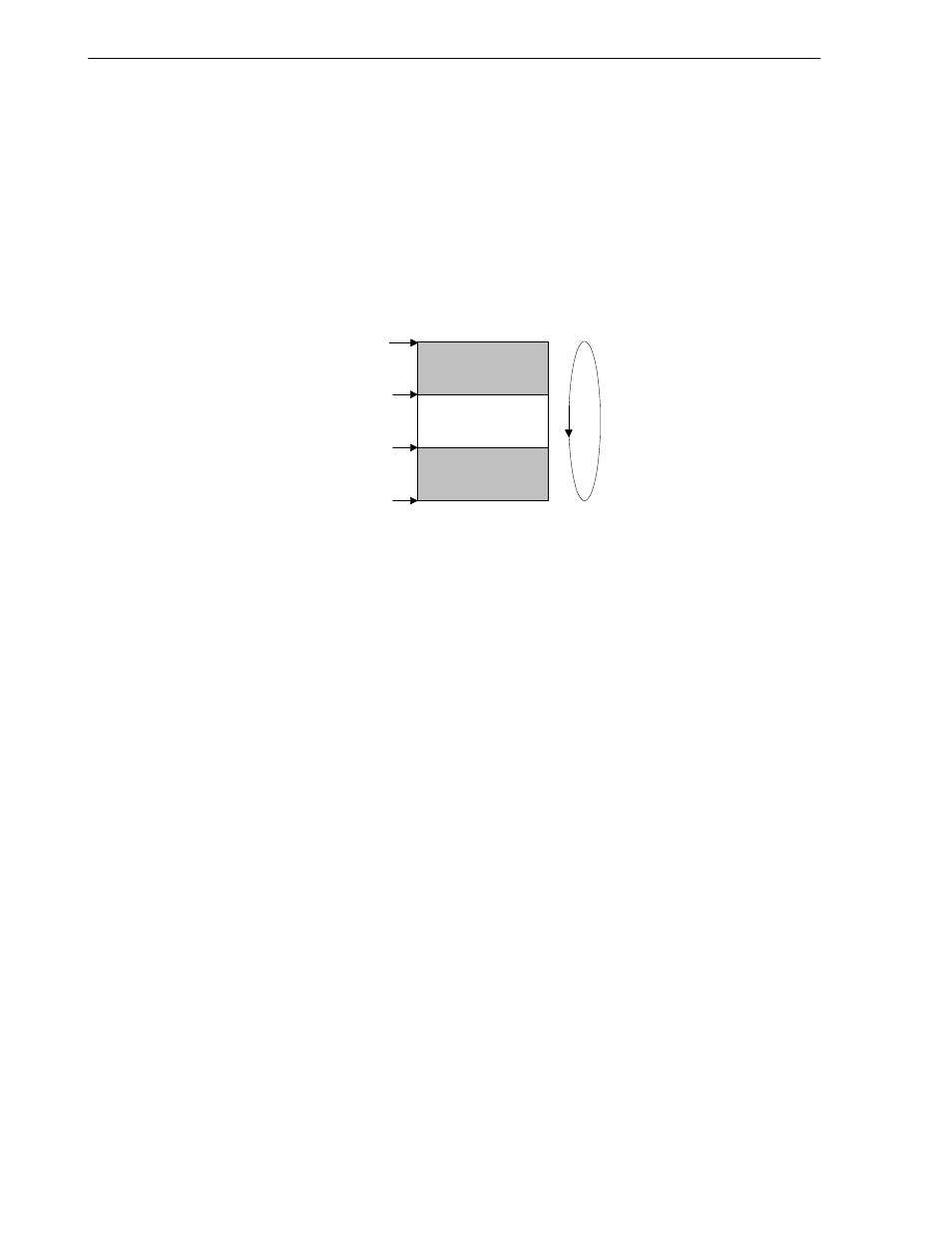

Figure 4-35. Mailbox Structure

A_MSA[3:0]

A_MWA[3:0]

A_MTA[3:0]

A_MBA[3:0]

Upon writing an indication, increments the write pointer (A_MWA[3:0]), sets the MM bit for the corresponding

mailbox in the A_GSR register, and issues an interrupt if it is not masked. When updating the write pointer

(A_MWA[3:0]), ATM Cell Processor causes A_MWA[3:0] to jump to the start address (A_MSA[3:0]) if A_MWA[3:0]

has reached the bottom address (A_MBA[3:0]). To read an indication, V

R

4120A uses the read pointer (A_MTA[3:0]).

A_MTA[3:0] is managed by the V

R

4120A: Each time V

R

4120A reads an indication from the mailbox, it writes the

address of the next indication to the read pointer (A_MTA[3:0]). If the write pointer (A_MWA[3:0]) points to the same

address as that pointed to by the read pointer (A_MTA[3:0]), sets the MF bit of the A_GSR register that corresponds

to the mailbox to indicate that the mailbox is full (the MF state), and issues an interrupt if it is not masked. Once the

mailbox enters the MF state, ATM Cell Processor does not execute any commands.