5 cache state transition diagrams – NEC Network Controller uPD98502 User Manual

Page 173

CHAPTER 2 V

R

4120A

Preliminary User’s Manual S15543EJ1V0UM

173

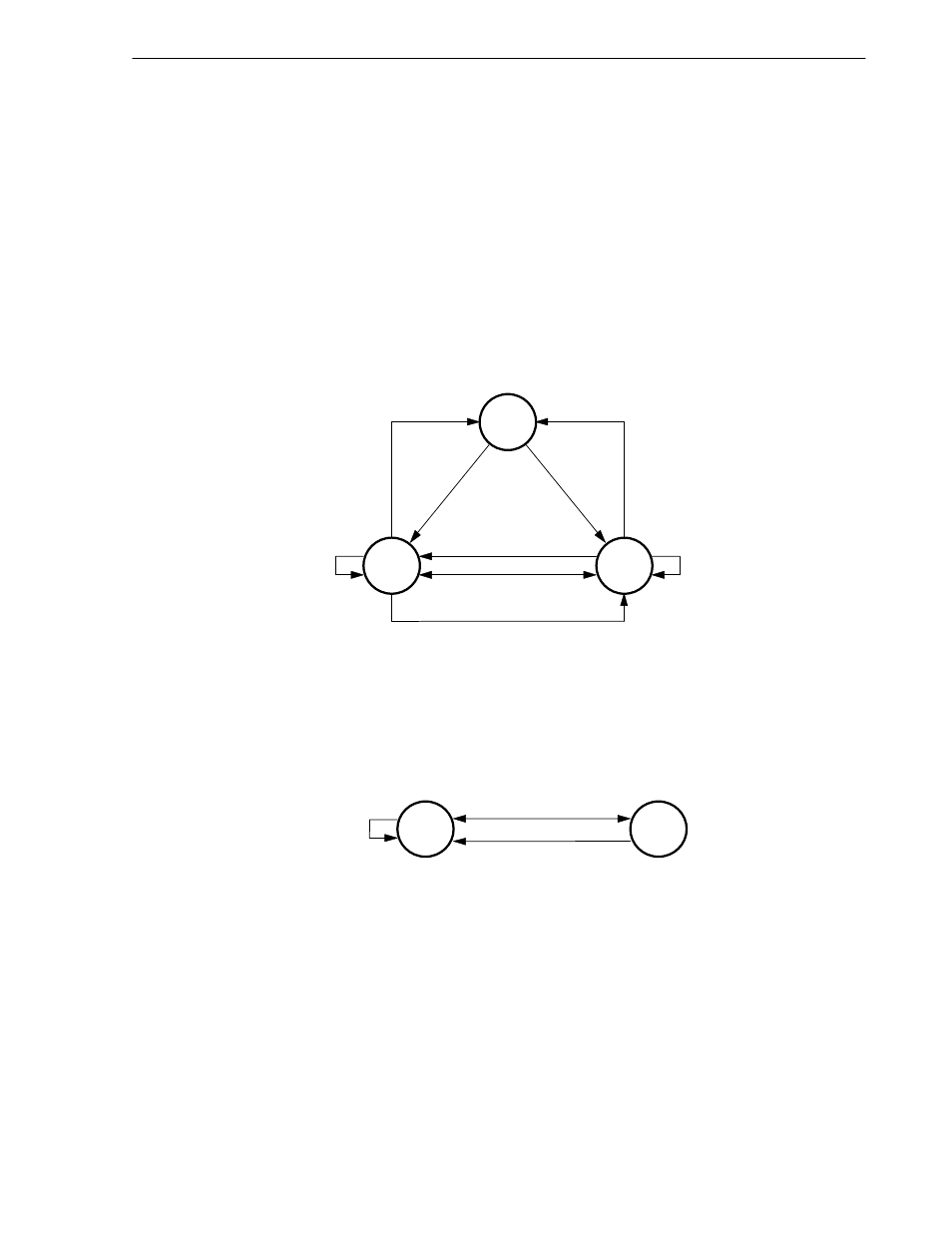

2.7.5 Cache state transition diagrams

The following section describes the cache state diagrams for the data and instruction cache lines. These state

diagrams do not cover the initial state of the system, since the initial state is system-dependent.

2.7.5.1 Data cache state transition

The following diagram illustrates the data cache state transition sequence. A load or store operation may include

one or more of the atomic read and write operations shown in the state diagram below, which may cause cache state

transitions.

Read (1) indicates a read operation from main memory to cache, inducing a cache state transition.

Read (2) indicates a read operation from cache to the CPU core, which induces no cache state transition.

Write (1) indicates a write operation from CPU core to cache, inducing a cache state transition.

Write (2) indicates a write operation from CPU core to cache, which induces no cache state transition.

Figure 2-70. Data Cache State Diagram

CACHE op

CACHE op

Write (1)

Write (1)

CACHE op

Write-back

Read (2)

Read (2)

Write (2)

Read (1)

Invalid

Valid

Dirty

Valid

Clean

2.7.5.2 Instruction cache state transition

The following diagram illustrates the instruction cache state transition sequence.

Read (1) indicates a read operation from main memory to cache, inducing a cache state transition.

Read (2) indicates a read operation from cache to the CPU core, which induces no cache state transition.

Figure 2-71. Instruction Cache State Diagram

Read (1)

CACHE op

Read (2)

Valid

Invalid