NEC Network Controller uPD98502 User Manual

Page 280

CHAPTER 5 ETHERNET CONTROLLER

280

Preliminary User’s Manual S15543EJ1V0UM

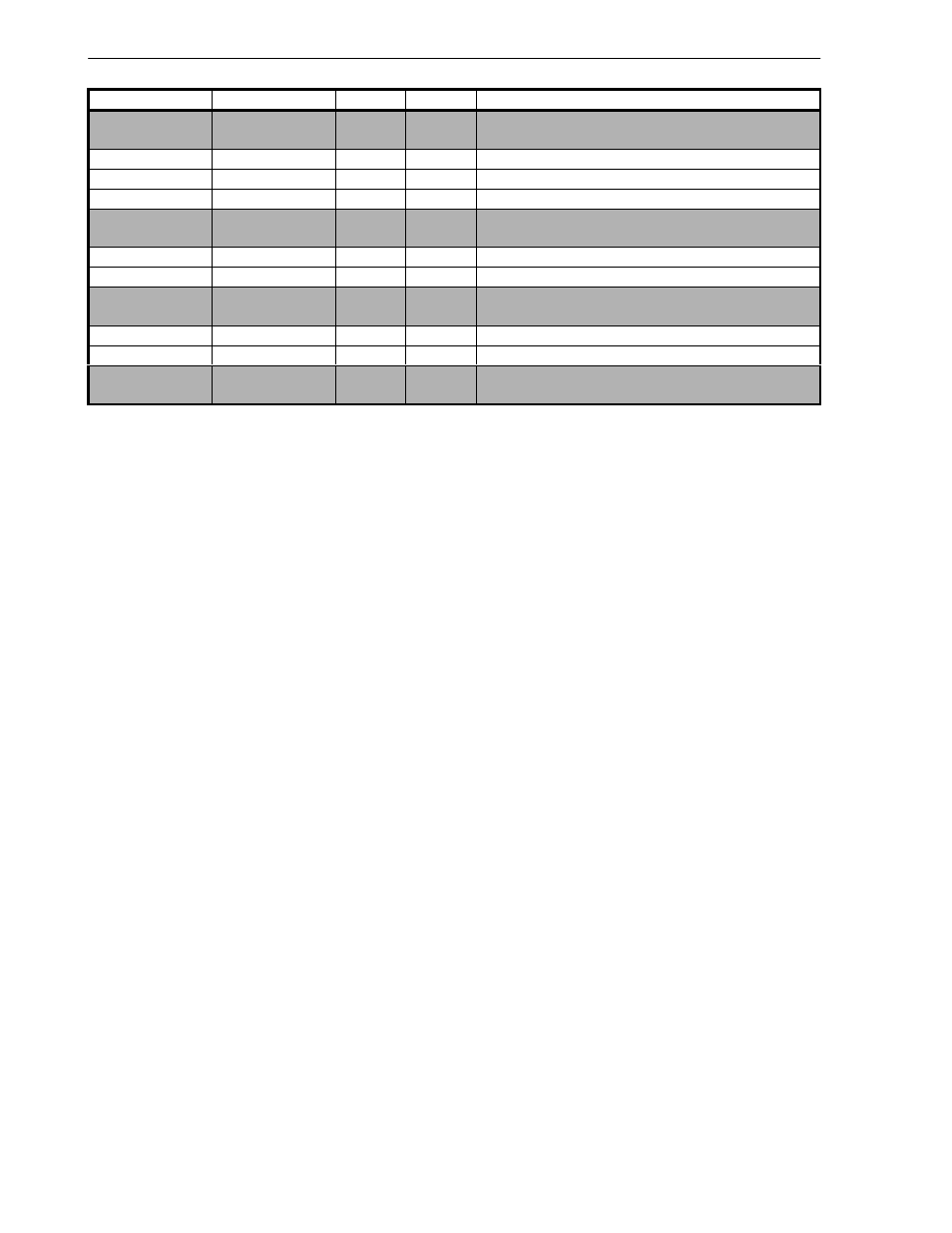

Offset Address

Register Name

R/W

Access

Description

1000_m0A8H:

1000_m0C4H

N/A

-

-

Reserved for future use

1000_m0C8H

En_AFR

R/W

W

Address Filtering Register

1000_m0CCH

En_HT1

R/W

W

Hash Table Register 1

1000_m0D0H

En_HT2

R/W

W

Hash Table Register 2

1000_m0D4H:

1000_m0D8H

N/A

-

-

Reserved for future use

1000_m0DCH

En_CAR1

R/W

W

Carry Register 1

1000_m0E0H

En_CAR2

R/W

W

Carry Register 2

1000_m0E4H:

1000_m012CH

N/A

-

-

Reserved for future use

1000_m130H

En_CAM1

R/W

W

Carry Mask Register 1

1000_m134H

En_CAM2

R/W

W

Carry Mask Register 2

1000_m138H:

1000_m13CH

N/A

-

-

Reserved for future use

Remarks 1. In the “Offset Address” field and in the “Register Name” field,

Ethernet Controller #1: m = 2, n = 1,

Ethernet Controller #2: m = 3, n = 2

2. In the “R/W” field,

“W” means “writeable”,

“R” means “readable”,

“RC” means “read-cleared”,

“- “ means “not accessible”.

3. All internal registers are 32-bit word-aligned registers.

4. The burst access to the internal register is prohibited.

If such burst access has been occurred, IRERR bit in NSR is set and NMI will assert to CPU.

5. Read access to the reserved area will set the CBERR bit in the NSR register and the dummy read

response data with the data-error bit set on SysCMD [0] is returned.

6. Write access to the reserved area will set the CBERR bit in the NSR register, and the write data is lost.

7. In the “Access” filed,

“W” means that word access is valid,

“H” means that half word access is valid,

“B” means that byte access is valid.

8. Write access to the read-only register cause no error, but the write data is lost.

9. The CPU can access all internal registers, but IBUS master device cannot access them.

5.2.1.2 Statistics counter registers

MAC Control Block gathers statistical information about the receive and transmit operations from the statistics

counters.

Each counter consists of 32-bit counter. When a counter overflow condition occurs, the corresponding bit of the

En_CAR1 register or En_CAR2 register is set to a 1, and it will generate an interrupt. The interrupt can be masked by

setting the bits of En_CAM1 register or En_CAM2 register.

A moment is required to complete the updating of all statistics counters after the change of the status vector (TSV

or RSV) because of the count operation.