Standby – NEC Network Controller uPD98502 User Manual

Page 557

APPENDIX A MIPS III INSTRUCTION SET DETAILS

Preliminary User’s Manual S15543EJ1V0UM

557

STANDBY

Standby

STANDBY

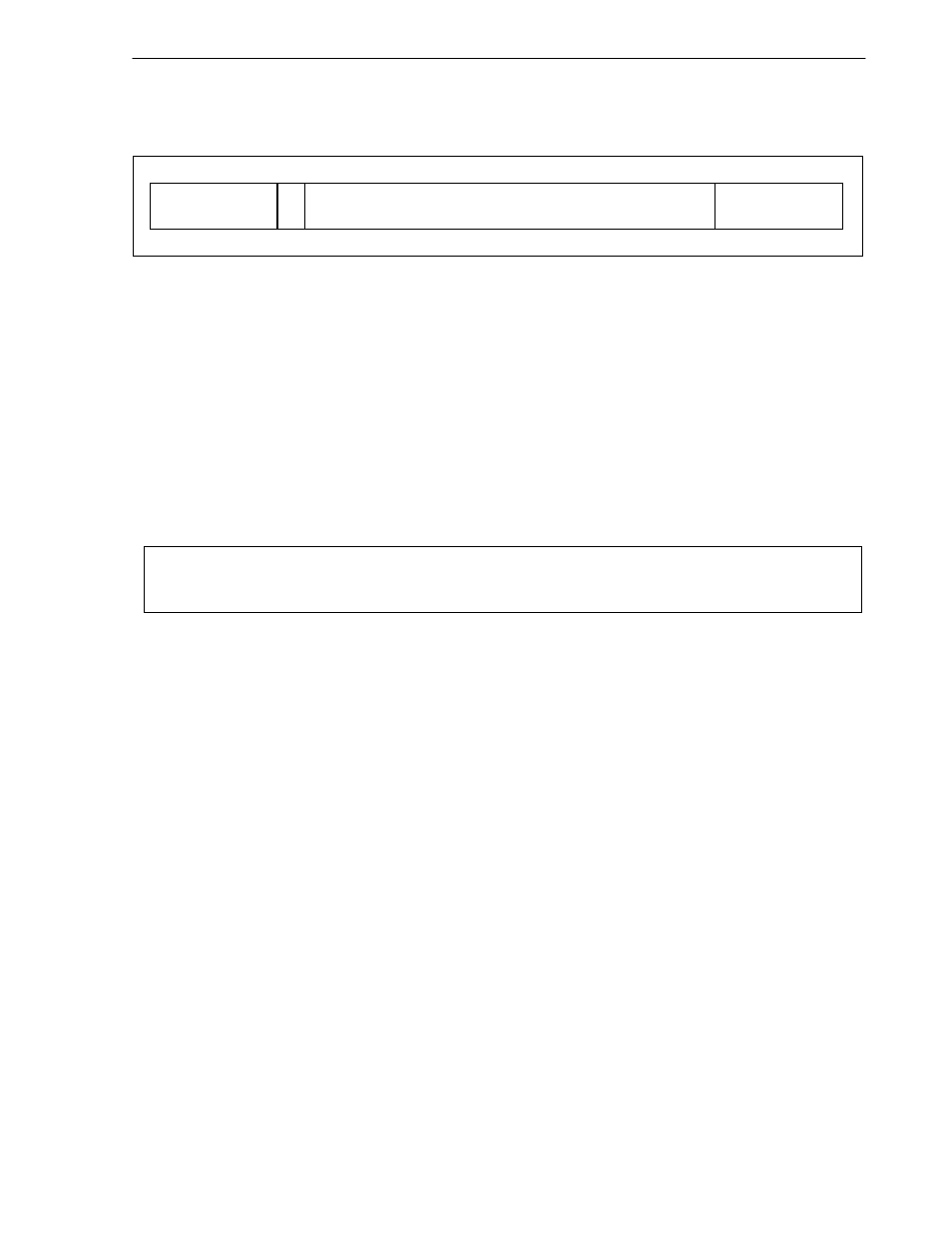

0

0 0 0 0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

COP0

0 1 0 0 0 0

STANDBY

1 0 0 0 0 1

31

26 25

6 5

0

6

19

6

CO

1

1

24

Format:

STANDBY

Description:

STANDBY instruction starts mode transition from Fullspeed mode to Standby mode.

When the STANDBY instruction finishes the WB stage, this processor wait by the SysAD bus is idle state, after

then the internal clocks will shut down, thus freezing the pipeline. The PLL, Timer/Interrupt clocks and the internal

bus clocks (TClock and MasterOut) will continue to run.

Once this processor is in Standby mode, any interrupt, including the internally generated timer interrupt, NMI, Soft

Reset, and Cold Reset will cause this processor to exit Standby mode and to enter Fullspeed mode.

Operation:

32, 64 T:

T+1: Standby operation ()

Exceptions:

Coprocessor unusable exception

Remark

Refer to Section 2.7.3.1 Power modes for details about the operation of the peripheral units at mode

transition.