7 s_ner (nmi enable register), 8 s_ver (version register) – NEC Network Controller uPD98502 User Manual

Page 195

CHAPTER 3 SYSTEM CONTROLLER

Preliminary User’s Manual S15543EJ1V0UM

195

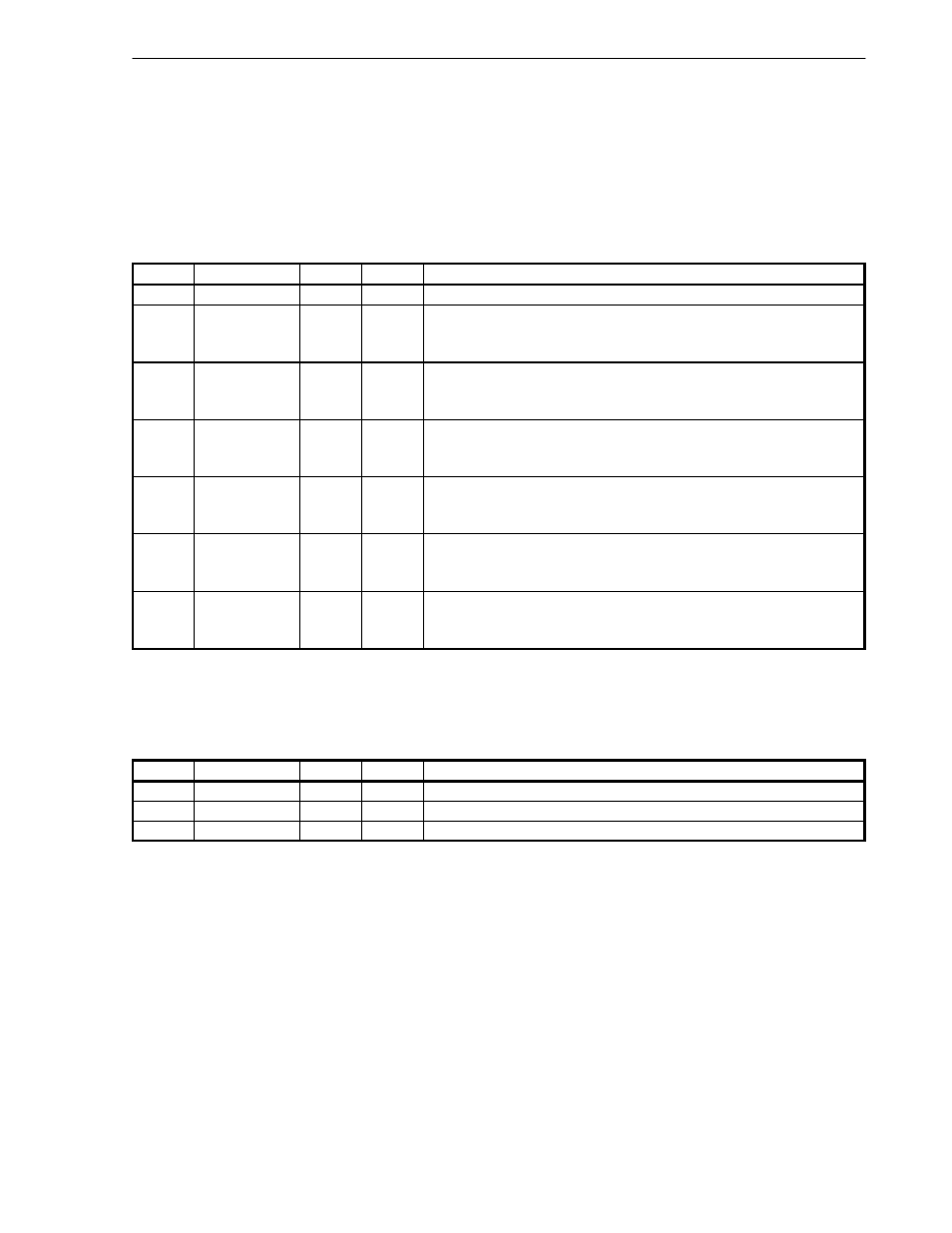

3.2.7 S_NER (NMI Enable Register)

The NMI enable register “S_NER” is a read-write and 32-bit word-aligned register. S_NER enables NMI for each

corresponding incident. A enable bit, which locates in the same bit location to a corresponding bit in S_NSR, controls

interruption triggered by the incident. If a bit of this register is reset to 0, the corresponding bit of the S_NSR is

disabled. If it is set to 1, the corresponding bit is enabled. When the enable bit is set and the bit in S_NSR is set,

system controller asserts interrupt signal to V

R

4120A. S_NER is initialized to 0 at reset and contains the following

fields:

Bits

Field

R/W

Default

Description

31:6

Reserved

R/W

0

Hardwired to 0.

5

IRERRE

R/W

0

Illegal internal register access error enable:

1 = enable.

0 = disable.

4

EXTNMIE

R/W

0

External NMI enable:

1 = enable.

0 = disable.

3

MAERRE

R/W

0

Memory address error enable:

1 = enable.

0 = disable.

2

ITERRE

R/W

0

IBUS timeout error enable:

1 = enable.

0 = disable.

1

IBERRE

R/W

0

IBUS bus error enable:

1 = enable.

0 = disable.

0

CBERRE

R/W

0

CPU bus error enable:

1 = enable.

0 = disable.

3.2.8 S_VER (Version Register)

The version register “S_VER” is a read-only and 32-bit word-aligned register. S_VER indicates version number of

the

µPD98502. S_VER is initialized to 300H at reset and contains the following fields:

Bits

Field

R/W

Default

Description

31:16

Reserved

R

0

Hardwired to 0.

15:8

MAJOR

R

03H

Major revision. Hardwired to 03H.

7:0

MINOR

R

00H

Minor revision. Hardwired to 00H.