8 uartfcr (uart fifo control register) – NEC Network Controller uPD98502 User Manual

Page 419

CHAPTER 8 UART

Preliminary User’s Manual S15543EJ1V0UM

419

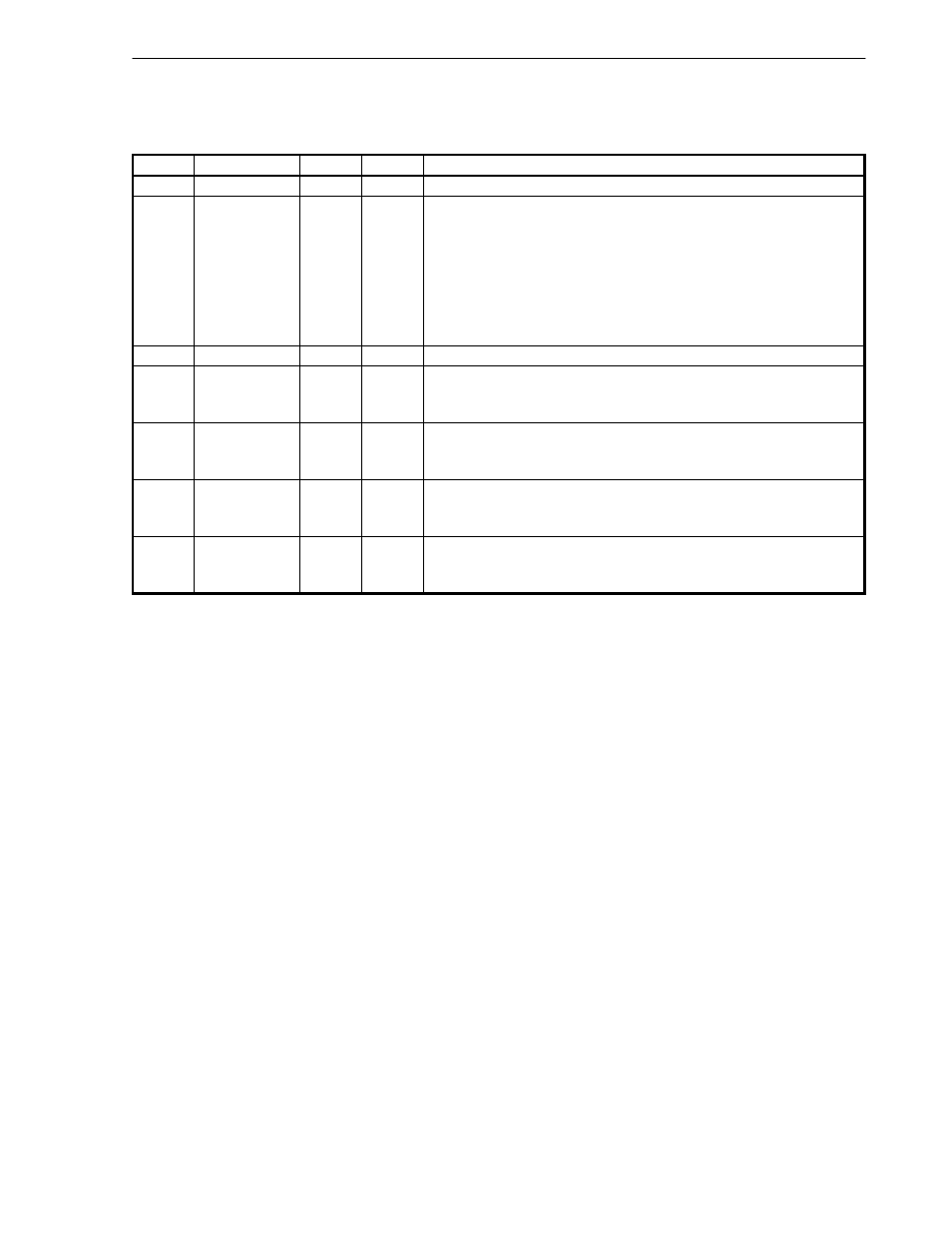

8.3.8 UARTFCR (UART FIFO Control Register)

This register is used to control the FIFOs: enable FIFO, clear FIFO, and set the receive FIFO trigger level.

Bits

Field

R/W

Default

Description

31:8

Reserved

W

0

Hardwired to 0.

7:6

URFTR

W

00

UART Receive FIFO Trigger level.

When the trigger level is reached, a Receive-buffer-Full interrupt is

generated, if enable by the ERBFI bit in the UARTIER. Number of bytes in

Receive FIFO is following.

00 = 1 byte

01 = 4 bytes

10 = 8 bytes

11 = 14 bytes

5:4

Reserved

W

0

Hardwired to 0.

3

FIFOMD

W

0

Switch between 16550 mode and FIFO mode

1 = From 16550 mode to FIFO mode

0 = From FIFO mode to 16550 mode

2

UTFRST

W

0

UART Transmitter FIFO Reset. (write-only)

1 = clear transmit FIFO and reset counter.

0 = no clear.

1

URFRST

W

0

UART Receiver FIFO Reset. (write-only)

1 = clear receive FIFO and reset counter.

0 = no clear.

0

UFIFOEN0

W

0

UART Receiver FIFO Enable. (write-only):

1 = enable receive and transmit FIFOs.

0 = disable and clear receive and transmit FIFOs.