NEC Network Controller uPD98502 User Manual

Page 190

CHAPTER 3 SYSTEM CONTROLLER

190

Preliminary User’s Manual S15543EJ1V0UM

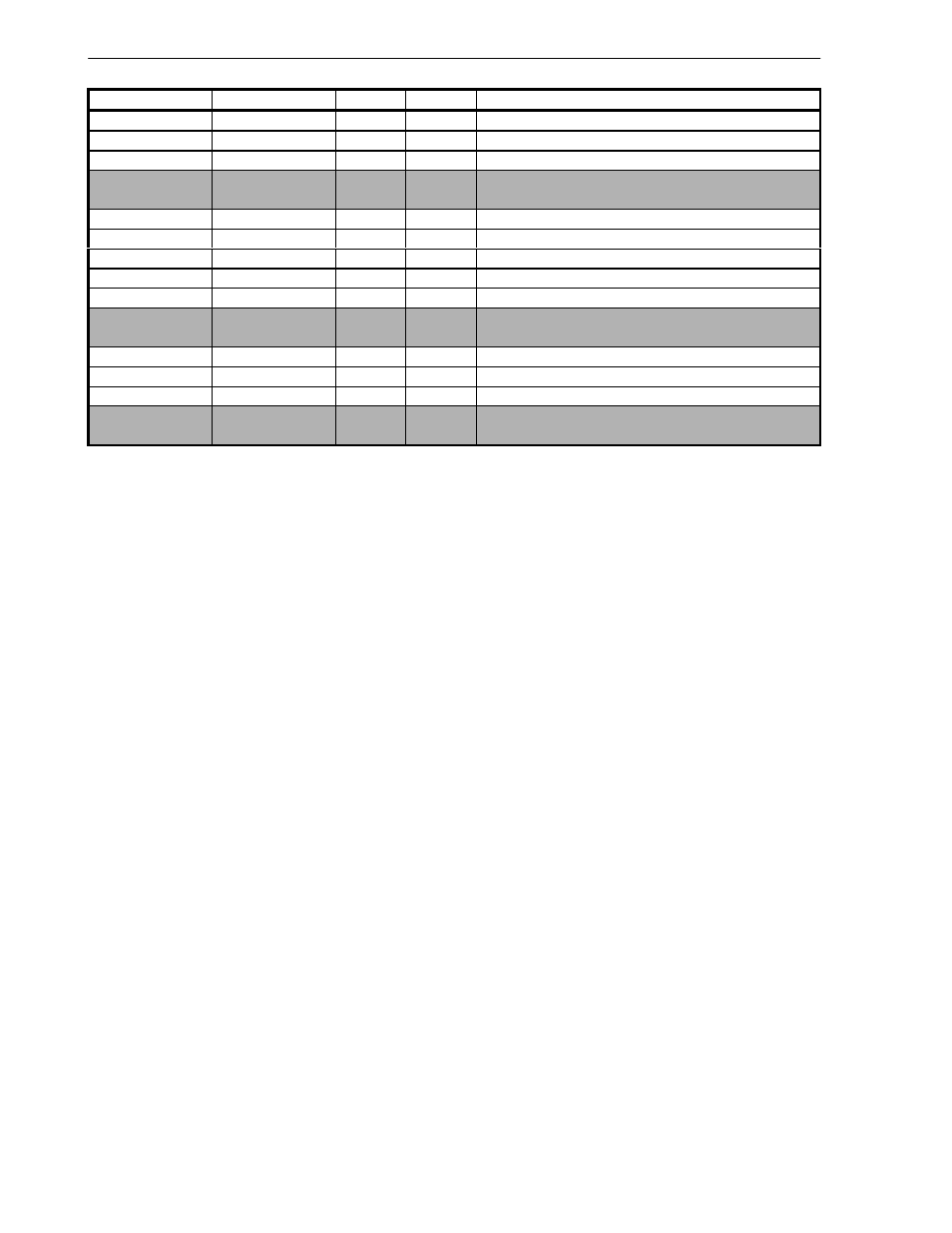

Offset Address

Register Name

R/W

Access

Description

1000_00D8H

MACAR1

R

W/H/B

MAC Address Register 1

1000_00DCH

MACAR2

R

W/H/B

MAC Address Register 2

1000_00E0H

MACAR3

R

W/H/B

MAC Address Register 3

1000_00E4H:

1000_00FCH

N/A

-

-

Reserved for future use

1000_0100H

RMMDR

R/W

W

Boot ROM Mode Register

1000_0104H

RMATR

R/W

W

Boot ROM Access Timing Register

1000_0108H

SDMDR

R/W

W

SDRAM Mode Register

1000_010CH

SDTSR

R/W

W

SDRAM Type Selection Register

1000_0110H

SDPTR

R/W

W

SDRAM Precharge Timing Register

1000_0114H:

1000_0118H

N/A

-

-

Reserved for future use

1000_011CH

SDRMR

R/W

W

SDRAM Refresh Mode Register

1000_0120H

SDRCR

R

W

SDRAM Refresh Timer Count Register

1000_0124H

MBCR

R/W

W

Memory Bus Control Register

1000_0128H:

1000_0FFCH

N/A

-

-

Reserved for future use

Remarks 1. In the “R/W” field,

“W” means “writeable”,

“R” means “readable”,

“RC” means “read-cleared”,

“- “ means “not accessible”.

2. All internal registers are 32-bit word-aligned registers.

3. The burst access to the internal register is prohibited.

If such burst access has been occurred, IRERR bit in NSR is set and NMI will assert to CPU.

4. Read access to the reserved area will set the CBERR bit in the NSR register and the dummy read

response data with the data-error bit set on SysCMD [0] is returned.

5. Write access to the reserved area will set the CBERR bit in the NSR register, and the write data is lost.

6. In the “Access” filed,

“W” means that word access is valid,

“H” means that half word access is valid,

“B” means that byte access is valid.

7. Write access to the read-only register cause no error, but the write data is lost.

8. The CPU can access all internal registers, but IBUS master device cannot access them.