4 a_imr (interrupt mask register) – NEC Network Controller uPD98502 User Manual

Page 241

CHAPTER 4 ATM CELL PROCESSOR

Preliminary User’s Manual S15543EJ1V0UM

241

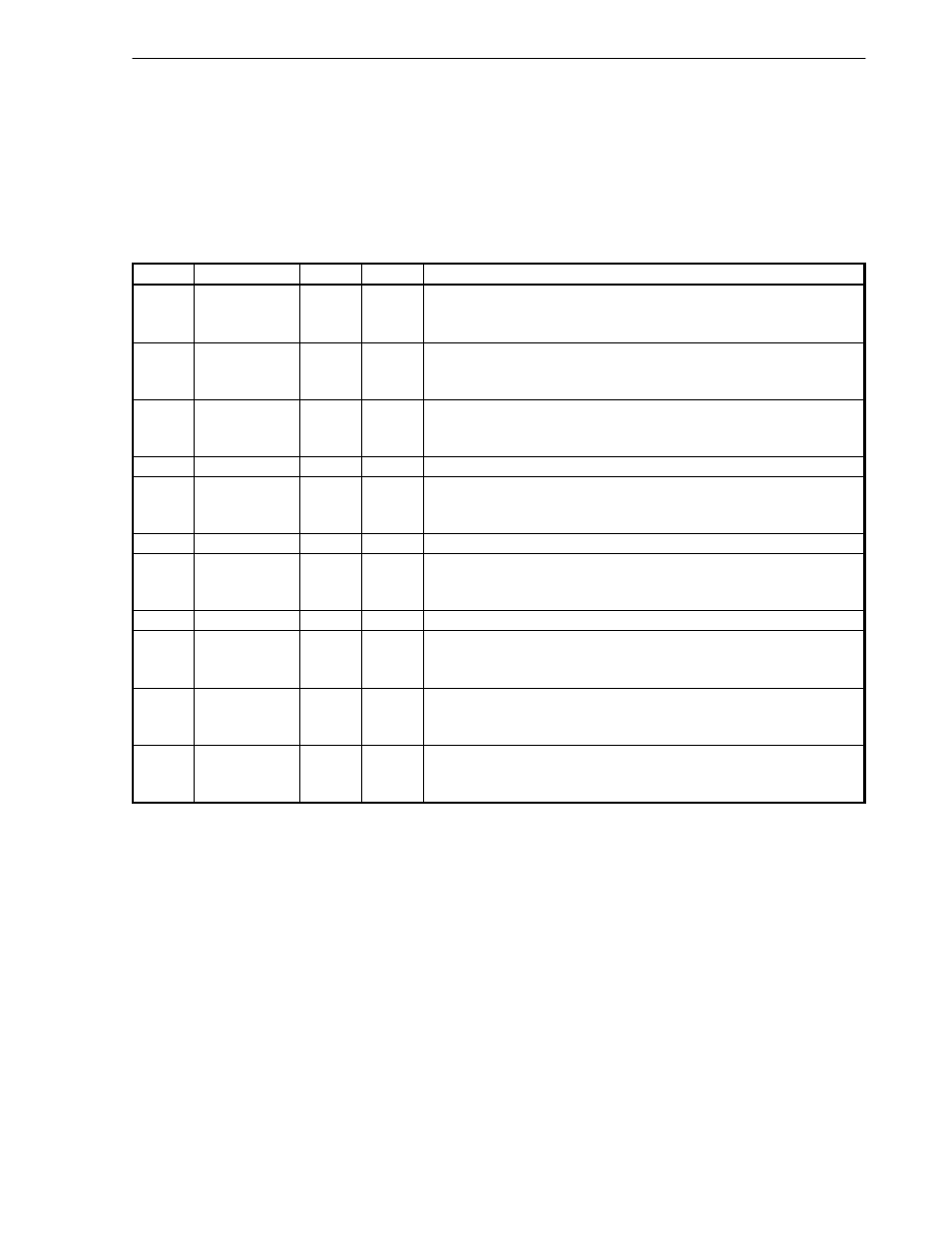

4.4.4 A_IMR (Interrupt Mask Register)

A_IMR masks interruption for each corresponding event. A Mask bit, which locates in the same bit location to a

corresponding bit in A_GSR, masks interruption. If a bit of this register is reset to a ‘0’, the corresponding bit of the

A_GSR is masked. If it is set to a ‘1’, the corresponding bit is unmasked. When the mask bit is reset and the bit in

A_GSR is set, an interruption is issued to V

R

4120A.

All bits of this register is writeable, but the bits 28-24, 22, 20-16 are reserved for future use.

Initial value is all zero.

Bits

Field

R/W

Default

Description

31

PI

R/W

0

Mask bit for PHY layer device interruption

0 = mask

1 = unmask

30

RQA

R/W

0

Mask bit for Receive Queue Alert

0 = mask

1 = unmask

29

RQU

R/W

0

Mask bit for Receive Queue underflow

0 = mask

1 = unmask

28:24

Reserved

R/W

0

Reserved for future use. Write ‘0’s.

23

SQO

R/W

0

Mask bit for Scheduling Queue overflow

0 = mask

1 = unmask

22

Reserved

R/W

0

Reserved for future use. Write ‘0’s.

21

FER

R/W

0

Mask bit for Fatal Error

0 = mask

1 = unmask

20:16

Reserved

R/W

0

Reserved for future use. Write ‘0’s.

15:8

RCR[7:0]

R/W

0

Mask bit for Raw cell reception

1 = Raw cell is in Pool No. [7:0]

0 = Raw cell is not in Pool No. [7:0]

7:4

MF[3:0]

R/W

0

Mask bit for Mailbox full

1 = Mailbox No. [3:0] is full

0 = Mailbox No. [3:0] is not full

3:0

MM[3:0]

R/W

0

Mask bit for Mailbox mark

1 = Mailbox No. [3:0] is marked

0 = Mailbox No. [3:0] is not marked