4 details of exceptions – NEC Network Controller uPD98502 User Manual

Page 142

CHAPTER 2 V

R

4120A

142

Preliminary User’s Manual S15543EJ1V0UM

2.5.4 Details of exceptions

This section describes causes, processes, and services of the V

R

4120A's exceptions.

2.5.4.1 Exception types

This section gives sample exception handler operations for the following exception types:

Cold Reset

Soft Reset

NMI

Remaining processor exceptions

When the EXL and ERL bits in the Status register are 0, either User, Supervisor, or Kernel operating mode is

specified by the KSU bits in the Status register. When either the EXL or ERL bit is set to 1, the processor is in Kernel

mode.

When the processor takes an exception, the EXL bit is set to 1, meaning the system is in Kernel mode. After

saving the appropriate state, the exception handler typically resets the EXL bit back to 0. The exception handler sets

the EXL bit to 1 so that the saved state is not lost upon the occurrence of another exception while the saved state is

being restored.

Returning from an exception also resets the EXL bit to 0. For details, see APPENDIX A MIPS III INSTRUCTION

SET DETAILS.

2.5.4.2 Exception vector address

The Cold Reset, Soft Reset, and NMI exceptions are always branched to the following reset exception vector

address. This address is in an uncached, unmapped space.

BFC0_0000H in 32-bit mode (virtual address)

FFFF_FFFF_BFC0_0000H in 64-bit mode (virtual address)

Vector addresses for the remaining exceptions are a combination of a vector offset and a base address.

64-/32-bit mode exception vectors and their offsets are shown below.

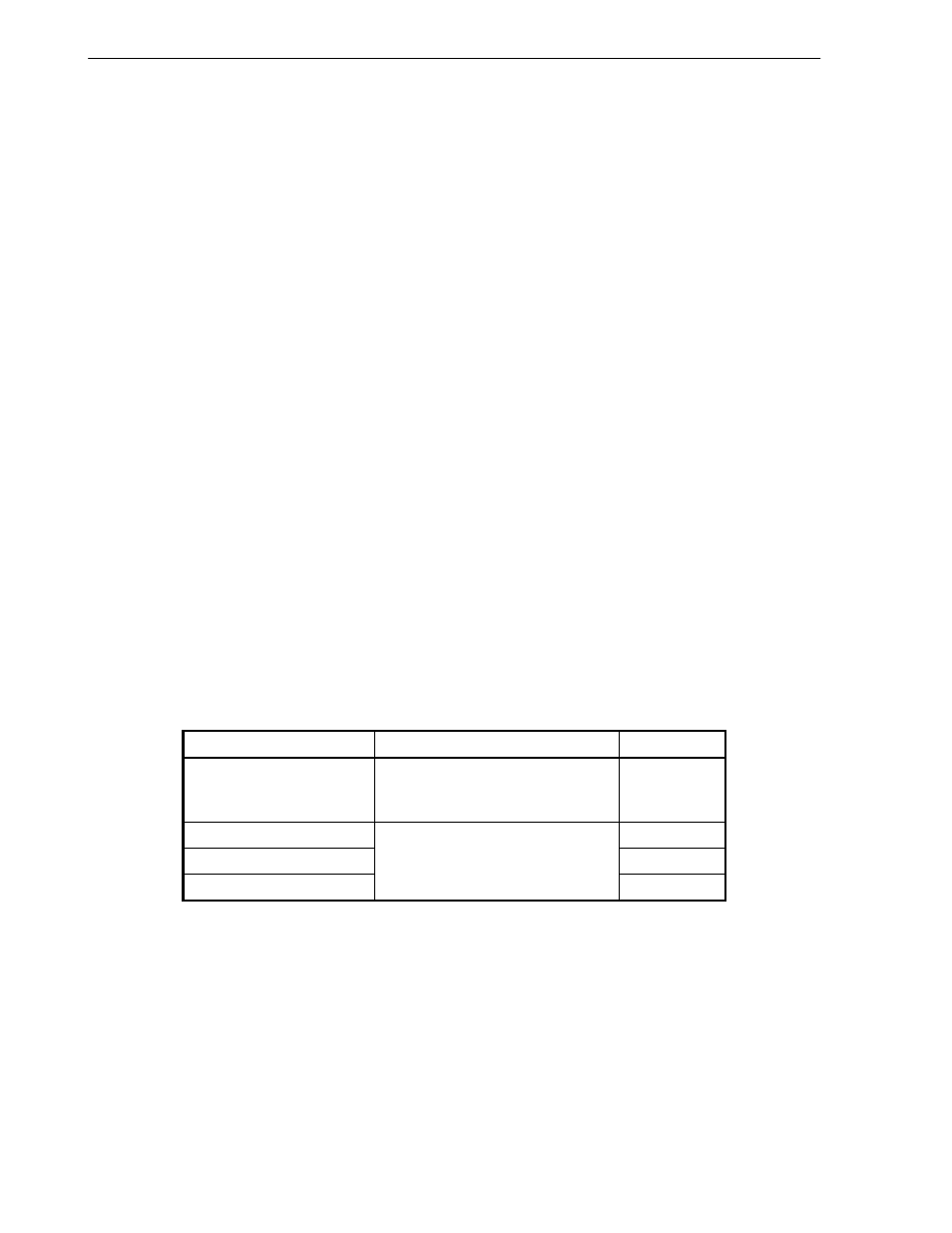

Table 2-36. 64-Bit Mode Exception Vector Base Addresses

Vector Base Address (Virtual)

Vector Offset

Cold Reset

Soft Reset

NMI

FFFF_FFFF_BFC0_0000H

(BEV bit is automatically set to 1)

0000H

TLB Refill (EXL = 0)

0000H

XTLB Refill (EXL = 0)

0080H

Other exceptions

FFFF_FFFF_8000_0000H (BEV = 0)

FFFF_FFFF_BFC0_0200H (BEV = 1)

0180H