13 boot rom – NEC Network Controller uPD98502 User Manual

Page 213

CHAPTER 3 SYSTEM CONTROLLER

Preliminary User’s Manual S15543EJ1V0UM

213

3.4.13 Boot ROM

The system controller supports up to 8 MB of boot memory. This memory must be populated with either of the

following two types of memory devices: PROM/flash memory.

3.4.13.1 Boot ROM configuration and address ranges

Boot ROM can be populated with PROM or 85-ns flash chips, and it must have an access time of 200 ns or less.

The system controller supports 8, 16 and 32-bit boot ROM at locations 1F80_0000H through 1FFF_FFFFH in the

physical memory space on V

R

4120A. The boot ROM does not support V

R

4120A cache operations.

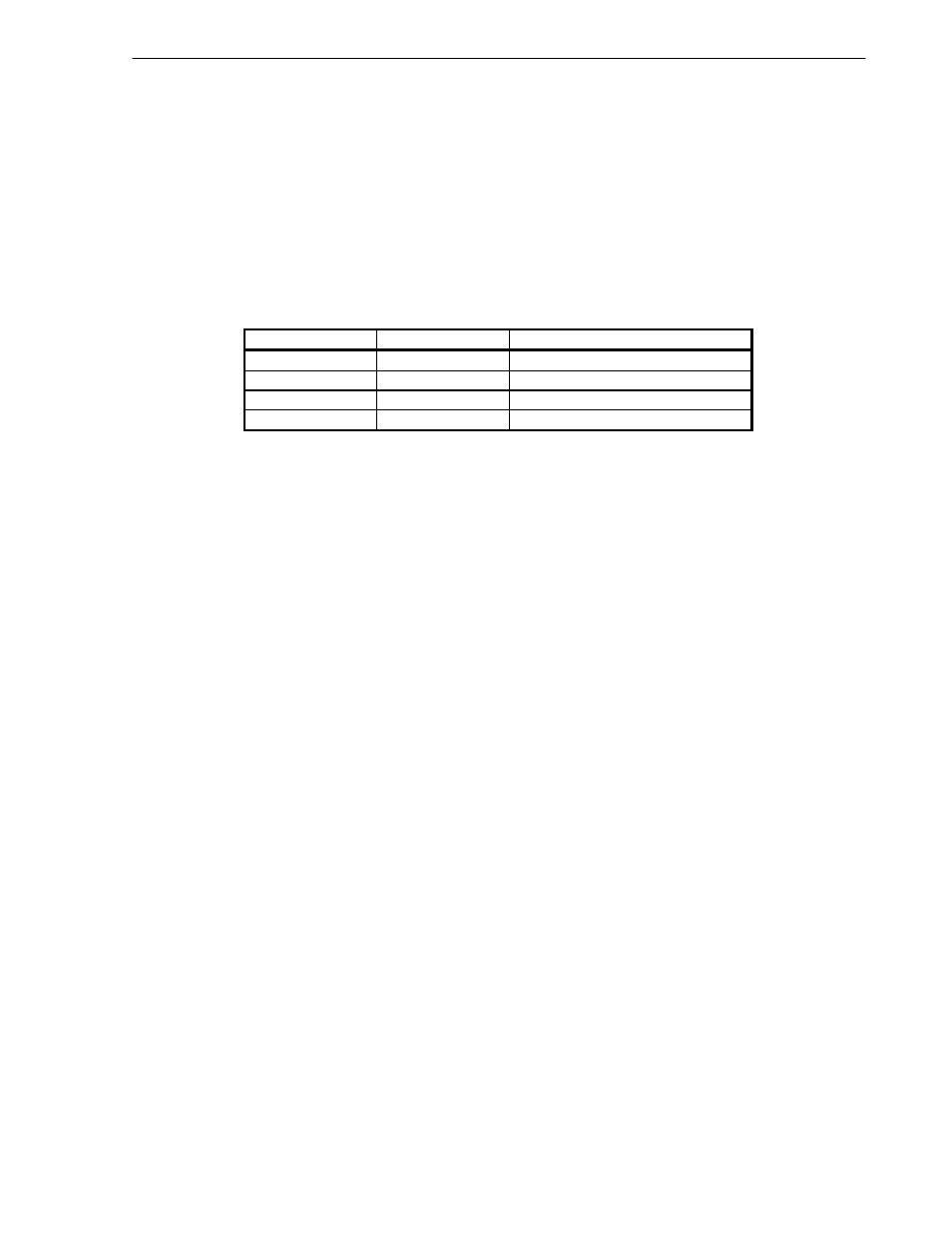

Table 3-6. Boot-ROM Size Configuration at Reset

RMMDR.FSM

Boot ROM Size

Address Range

00

4 MB

1FC0_0000H through 1FFF_FFFH

01

8 MB

1F80_0000H through 1FFF_FFFH

10

1 MB

1FC0_0000H through 1FCF_FFFH

11

2 MB

1FC0_0000H through 1FDF_FFFH

The controller asserts the flash/ROM chip select (SRMCS_B) in the address range 1F80_0000H through

1FFF_FFFFH. When writes are performed to the ROM/flash memory space, the controller asserts SDWE_B in

conjunction with SRMCS_B. When reads are performed, the controller asserts SRMOE_B in conjunction with

SRMCS_B. If the V

R

4120A attempts to access boot ROM addresses outside the defined size of the flash/ROM, the

controller returns 0 with the data error bit set on SysCMD [0]. In addition, the NMI status register “S_NSR” is updated

and NMI is asserted to V

R

4120A, if the interrupt is enabled in the NMI enable register “S_NER”.

3.4.13.2 Flash memory write-protection

The flash memory can be protected in software. Software protection is implemented by programming the WM field

in ROM mode register “RMMDR”.

3.4.13.3 Flash memory operations

Flash memory I/F has 3 modes for each Flash data BUS size, that is 8,16 and 32 bits. And on the case of each Bus

size, the way of causing write cycle will be changed. The flash memory can be programmed using following write

cycle sequence by V

R

4120A. The following commands are example of operations for the AMD AM29LV800BT flash

memory (using Byte Mode) at 32-bit Flash data Bus mode in System Controller.