11 uartlsr (uart line status register) – NEC Network Controller uPD98502 User Manual

Page 422

CHAPTER 8 UART

422

Preliminary User’s Manual S15543EJ1V0UM

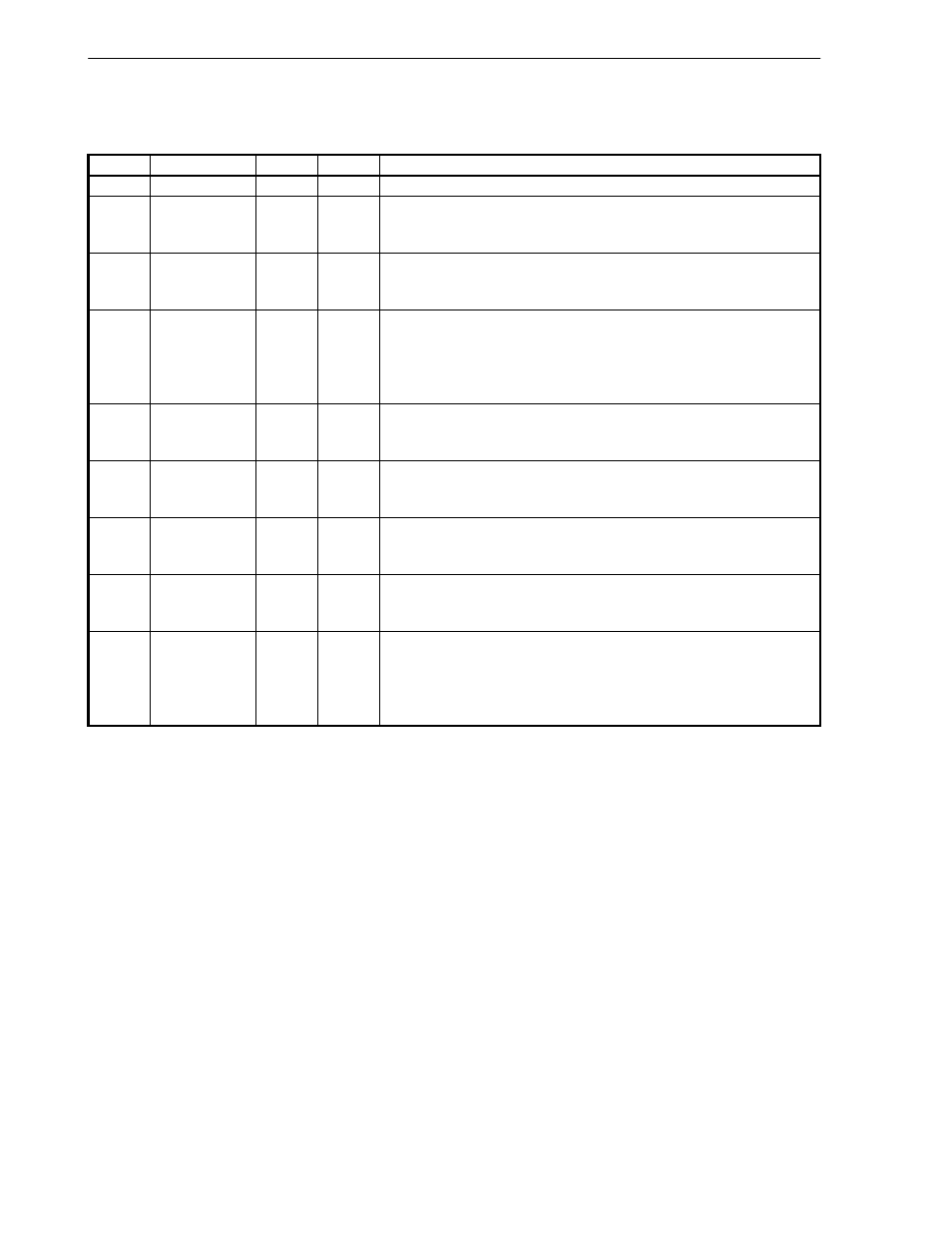

8.3.11 UARTLSR (UART Line Status Register)

This register reports the current state of the transmitter and receiver logic.

Bits

Field

R/W

Default

Description

31:8

Reserved

R/W

0

Hardwired to 0.

7

RFERR

R/W

0

Receiver FIFO Error.

1 = parity, framing, or break error in receiver buffer.

0 = no such error.

6

TEMT

R/W

1

Transmitter Empty.

1 = transmitter holding and shift registers empty.

0 = transmitter holding or shift register not empty.

5

THRE

R/W

1

Transmitter Holding Register Empty.

1 = transmitter holding register empty.

0 = transmitter holding register not empty.

Transmit data is stored in the UART Transmitter Data

Holding Register (UARTTHR)

4

BI

R/W

0

Break Interrupt.

1 = break received on URSDI signal.

0 = no break.

3

FE

R/W

0

Receive-Data Framing Error.

1 = framing error on receive data.

0 = no such error.

2

PE

R/W

0

Receive-Data Parity Error.

1 = parity error on receive data.

0 = no such error.

1

OE

R/W

0

Receive-Data Overrun Error.

1 = overrun error on receive data.

0 = no such error.

0

DR

R/W

0

Receive-Data Ready.

1 = receive data buffer full.

0 = receive data buffer not full.

Receive data is stored in the UART Receiver Data Buffer Register

(UARTRBR).