Load doubleword right (3/3) – NEC Network Controller uPD98502 User Manual

Page 510

APPENDIX A MIPS III INSTRUCTION SET DETAILS

510

Preliminary User’s Manual S15543EJ1V0UM

LDR

Load Doubleword Right (3/3)

LDR

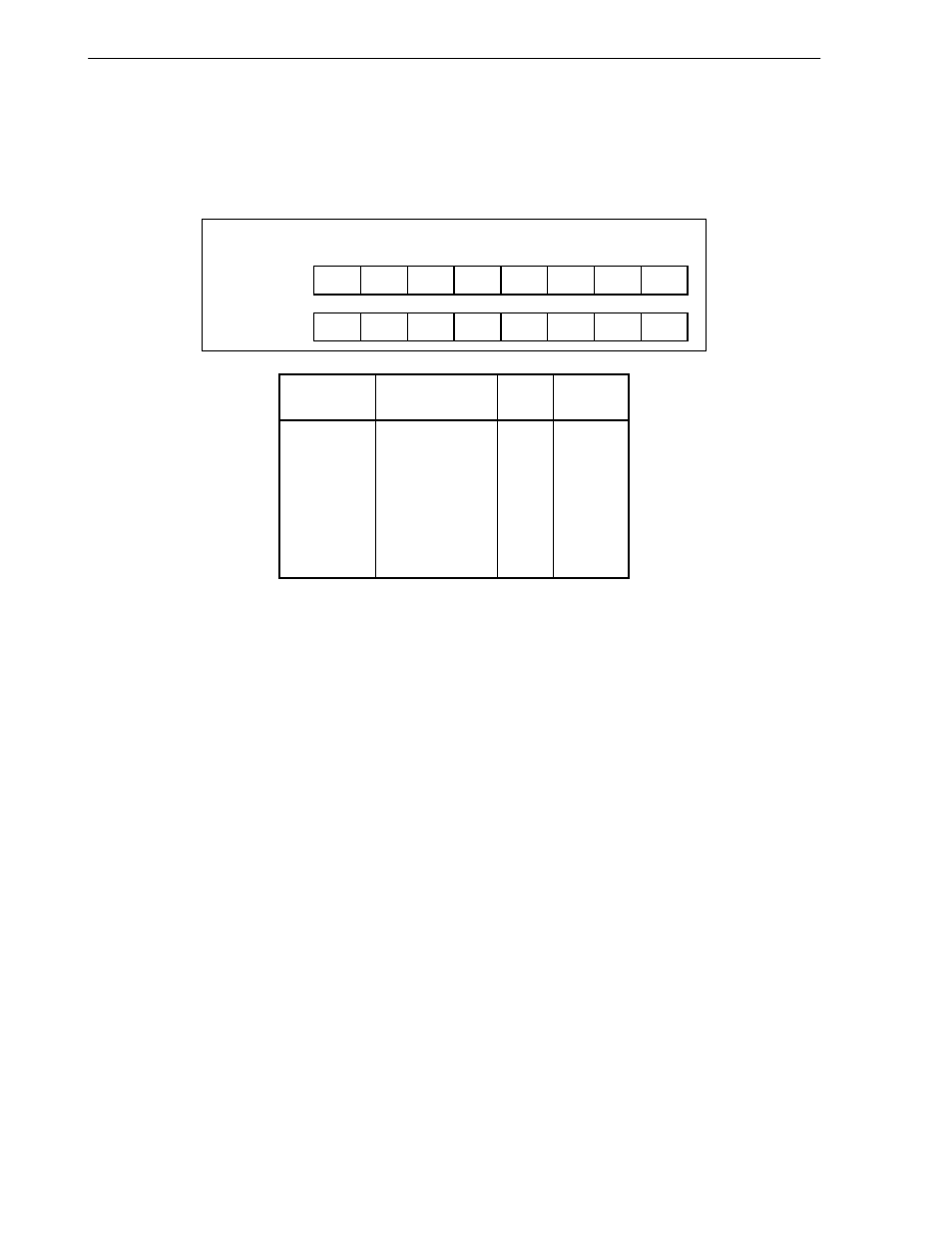

Given a doubleword in a register and a doubleword in memory, the operation of LDR is as follows:

B

C

D

E

F

G

A

H

J

K

L

M

N

O

I

P

Register

Memory

LDR

vAddr2..0

Destination

Type

Offset

(LEM)

0

1

2

3

4

5

6

7

I J K L MN O P

A I J K L M N O

A B I J K L M N

A B C I J K L M

A B C D I J K L

A B C D E I J K

A B C D E F I J

A B C D E F G I

7

6

5

4

3

2

1

0

0

1

2

3

4

5

6

7

Remark

LEM

Little-endian memory (BigEndianMem = 0)

Type

AccessType (see Table 2-3. Byte Specification Related to Load and Store Instructions)

sent to memory

Offset

pAddr2..0 sent to memory

Exceptions:

TLB refill exception

TLB invalid exception

Bus error exception

Address error exception

Reserved instruction exception (32-bit user mode/supervisor mode)