30 en_rxfcr (receive fifo control register), 31 en_rxdpr (receive descriptor pointer) – NEC Network Controller uPD98502 User Manual

Page 297

CHAPTER 5 ETHERNET CONTROLLER

Preliminary User’s Manual S15543EJ1V0UM

297

5.2.30 En_RXFCR (Receive FIFO Control Register)

Bits

Field

R/W

Default

Description

31:26

UWM

[7:2]

R/W

30H

Upper Water Mark:

This pointer is used with Auto Flow Control Enable bit in En_TXCR. When

the receiving data fill level exceeds this pointer, the transmit module

generates a flow control frame automatically.

25:24

Reserved

R/W

0

Reserved for future use. Write 0s.

23:18

LWN

[7:2]

R/W

10H

Lower Water Mark:

17:8

Reserved

R/W

0

Reserved for future use. Write 0s.

7:2

RX_DRTH

R/W

10H

Receive Drain Threshold Level

This threshold is enable to the transmit data to the IBUS via internal DMAC

form the FIFO. Please see the Figure 5-3. This pointer is a word pointer.

1:0

Reserved

R/W

0

Reserved for future use. Write 0s.

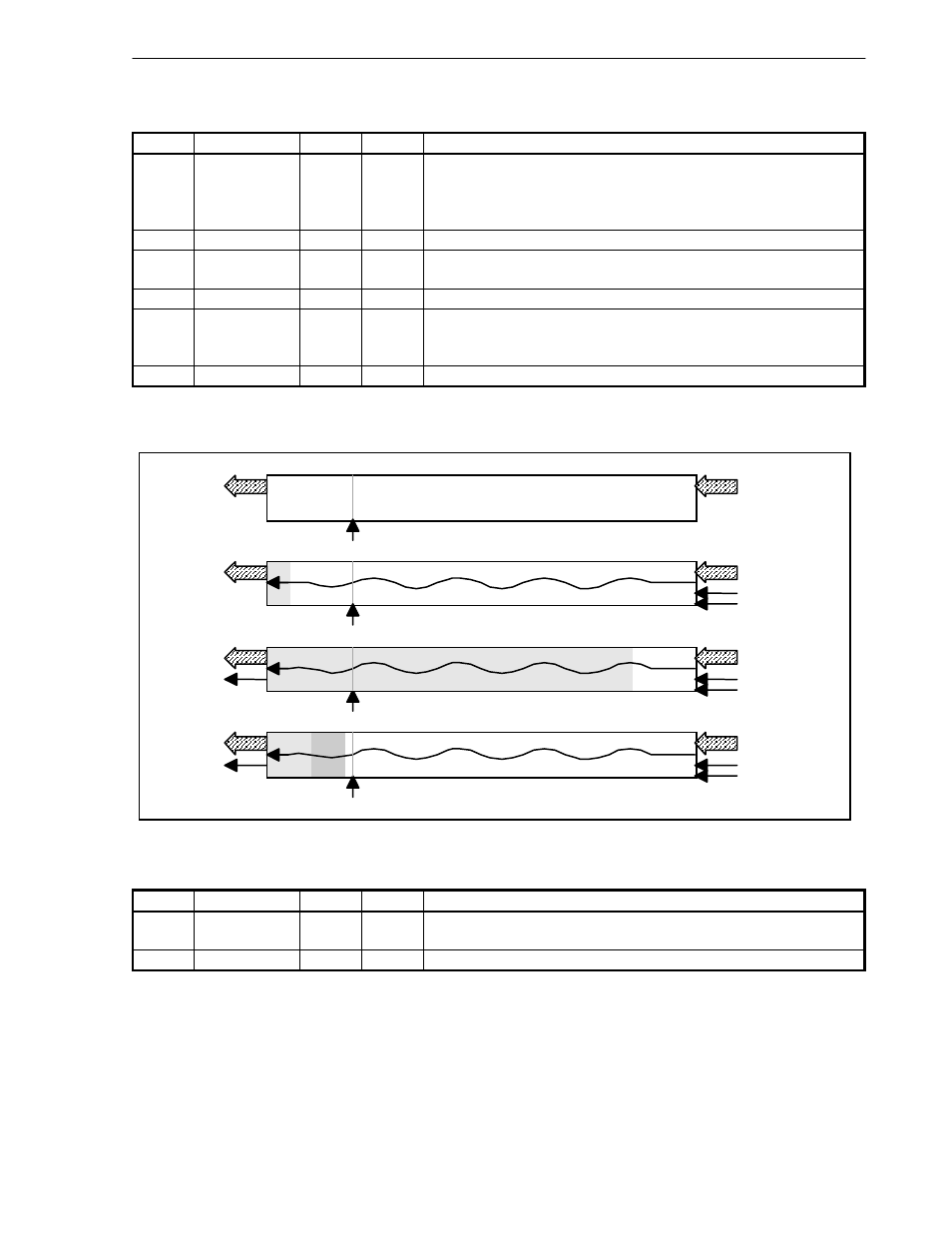

Figure 5-3. Rx FIFO Control Mechanism

DRTH

DRTH

DRTH

Rx_FIFO (256 Bytes)

DRTH

EOF

No Packet

data

Beginning

of the

frame

Request

to transmit

data

Request

to transmit

data

Receiving

frame

Received

End of frame

To internal bus

From MAC Control Block

5.2.31 En_RXDPR (Receive Descriptor Pointer)

Bits

Field

R/W

Default

Description

31:2

RCVDP

R/W

0

Receive Descriptor Pointer:

Please see the Section 5.3.5.

1:0

Reserved

R/W

0

Reserved for future use. Write 0s.