NEC Network Controller uPD98502 User Manual

Page 589

APPENDIX A MIPS III INSTRUCTION SET DETAILS

Preliminary User’s Manual S15543EJ1V0UM

589

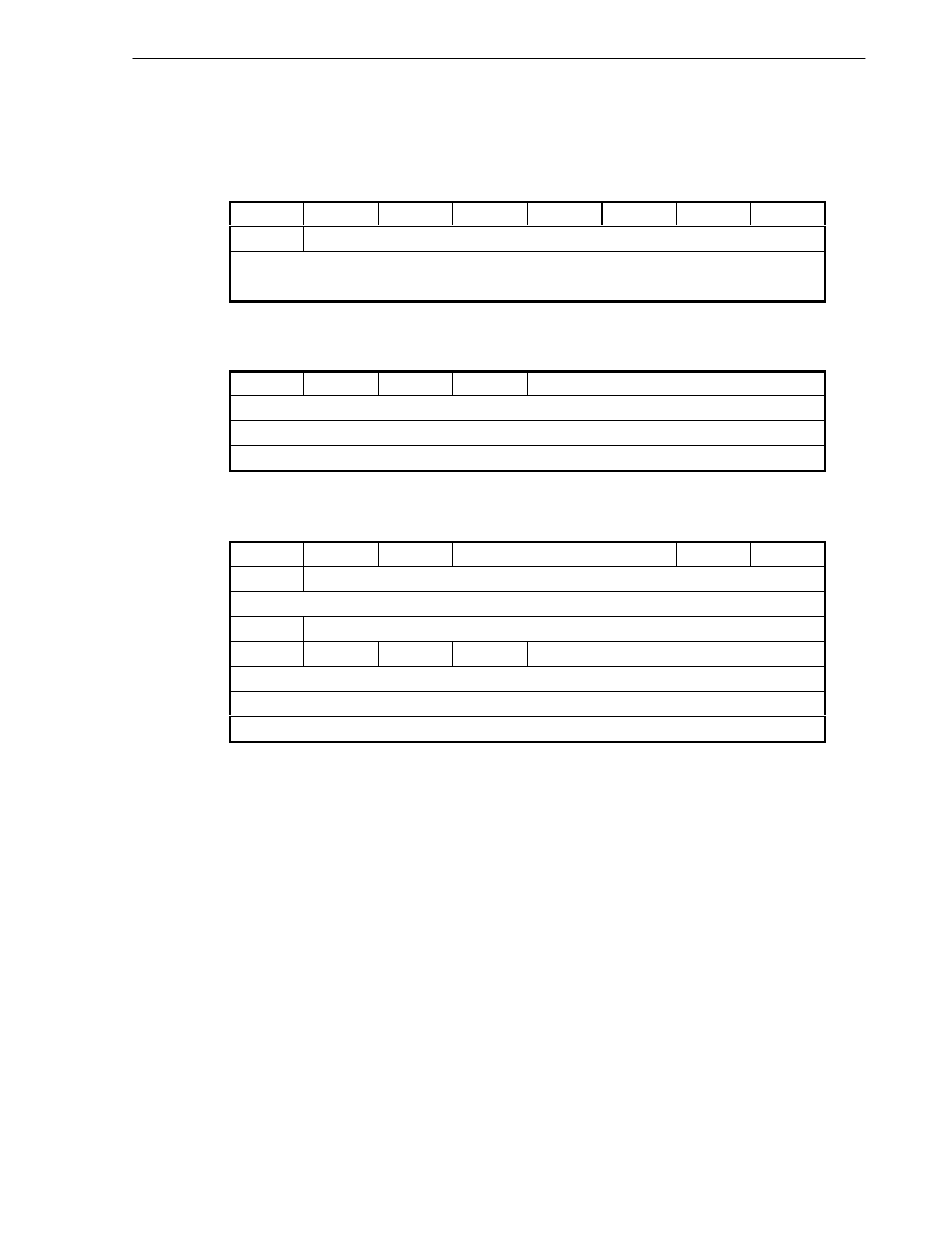

Figure A-1. V

R

4120AOpcode Bit Encoding (2/2)

23...21

COP0 rs

25, 24

0

1

2

3

4

5

6

7

0

MF

DMF

ε

γ

γ

MT

DMT

ε

γ

γ

1

BC

γ

γ

γ

γ

γ

γ

γ

2

CO

3

18...16

COP0 rt

20...19

0

1

2

3

4

5

6

7

0

BCF

BCT

BCFL

BCTL

γ

γ

γ

γ

1

γ

γ

γ

γ

γ

γ

γ

γ

2

γ

γ

γ

γ

γ

γ

γ

γ

3

γ

γ

γ

γ

γ

γ

γ

γ

2...0

CP0 Function

5...3

0

1

2

3

4

5

6

7

0

φ

TLBR

TLBWI

φ

φ

φ

TLBWR

φ

1

TLBP

φ

φ

φ

φ

φ

φ

φ

2

ξ

φ

φ

φ

φ

φ

φ

φ

3

ERET

χ

φ

φ

φ

φ

φ

φ

φ

4

φ

STANDBY

SUSPEND HIBERNAT

φ

φ

φ

φ

5

φ

φ

φ

φ

φ

φ

φ

φ

6

φ

φ

φ

φ

φ

φ

φ

φ

7

φ

φ

φ

φ

φ

φ

φ

φ

Key:

*

Operation codes marked with an asterisk cause reserved instruction exceptions in all current

implementations and are reserved for future versions of the architecture.

γ Operation codes marked with a gamma cause a reserved instruction exception. They are reserved for future

versions of the architecture.

δ Operation codes marked with a delta are valid only for V

R

4400 Series processors with CP0 enabled, and

cause a reserved instruction exception on other processors.

φ Operation codes marked with a phi are invalid but do not cause reserved instruction exceptions in V

R

4121

implementations.

ξ Operation codes marked with a xi cause a reserved instruction exception on V

R

4121 processor.

χ Operation codes marked with a chi are valid on V

R

4000 Series only.

ε Operation codes marked with epsilon are valid when the processor operating as a 64-bit processor. These

instructions will cause a reserved instruction exception if 64-bit operation is not enabled.

π Operation codes marked with a pi are invalid and cause coprocessor unusable exception.

θ Operation codes marked with a theta are valid when MIPS16 instruction execution is enabled, and cause a

reserved instruction exception when MIPS16 instruction execution is disabled.