Bc0tl, Branch on coprocessor 0 true likely (1/2) – NEC Network Controller uPD98502 User Manual

Page 446

APPENDIX A MIPS III INSTRUCTION SET DETAILS

446

Preliminary User’s Manual S15543EJ1V0UM

BC0TL

Branch On Coprocessor 0 True Likely (1/2)

BC0TL

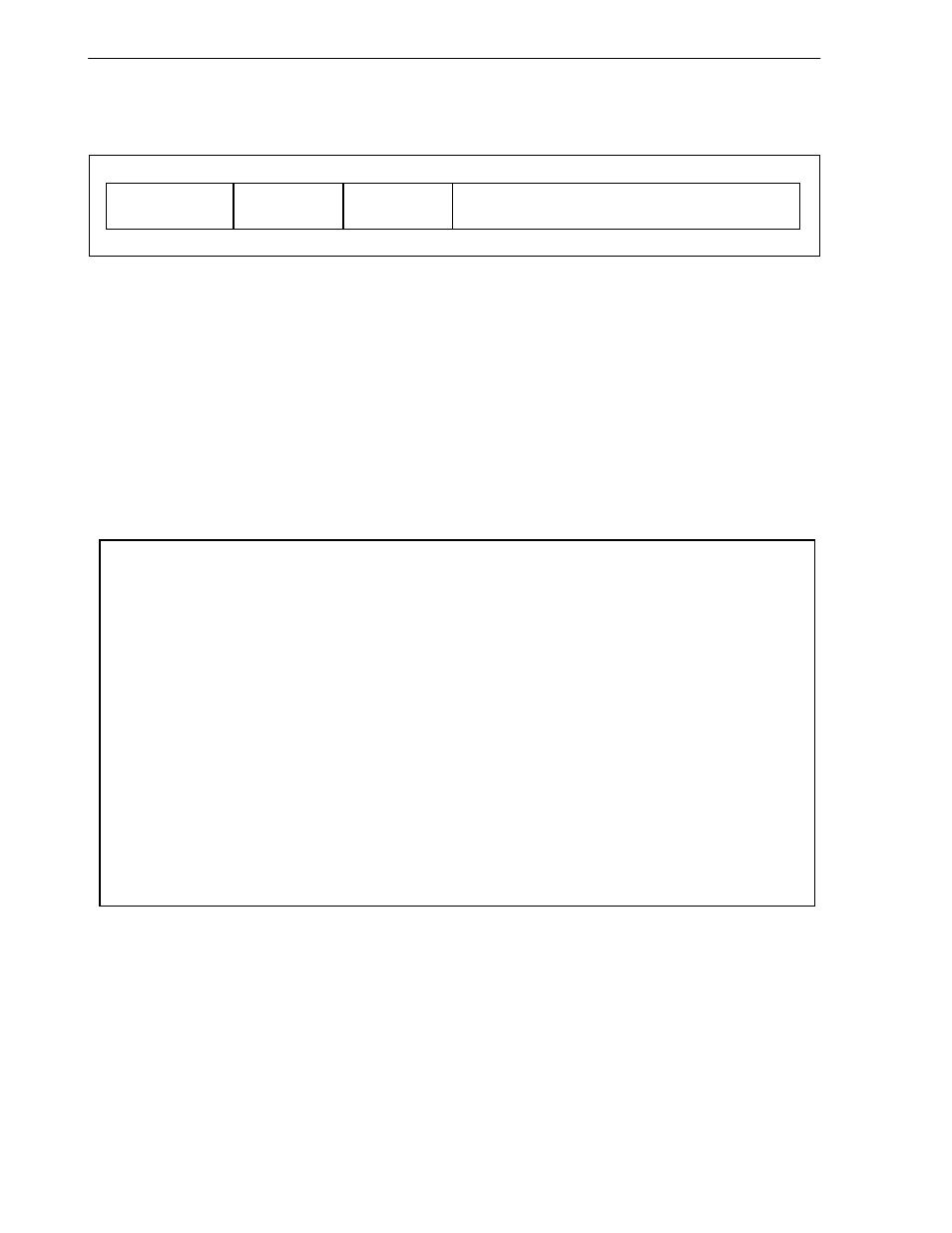

BC

0 1 0 0 0

COPz

0 1 0 0 X X

Note

BCTL

0 0 0 1 1

offset

31

26 25

21 20

16 15

0

6

5

5

16

Format:

BC0TL offset

Description:

A branch target address is computed from the sum of the address of the instruction in the delay slot and the 16-bit

offset, shifted left two bits and sign-extended. If the contents of CP0's condition (CpCond) line, as sampled during

the previous instruction, is true, the target address is branched to with a delay of one instruction.

If the conditional branch is not taken, the instruction in the branch delay slot is nullified.

Because the condition line is sampled during the previous instruction, there must be at least one instruction

between this instruction and a coprocessor instruction that changes the condition line.

Operation:

32

T-1:

condition

← SR

18

T:

target

← (offset

15

)

14

|| offset || 0

2

T+1: if condition then

PC

← PC + target

else

NullifyCurrentInstruction

endif

64

T-1:

condition

← SR

18

T:

target

← (offset

15

)

46

|| offset || 0

2

T+1: if condition then

PC

← PC + target

else

NullifyCurrentInstruction

endif

Exceptions:

Coprocessor unusable exception

Note See the opcode table below, or A.6 CPU Instruction Opcode Bit Encoding.