NEC Network Controller uPD98502 User Manual

Page 80

CHAPTER 2 V

R

4120A

80

Preliminary User’s Manual S15543EJ1V0UM

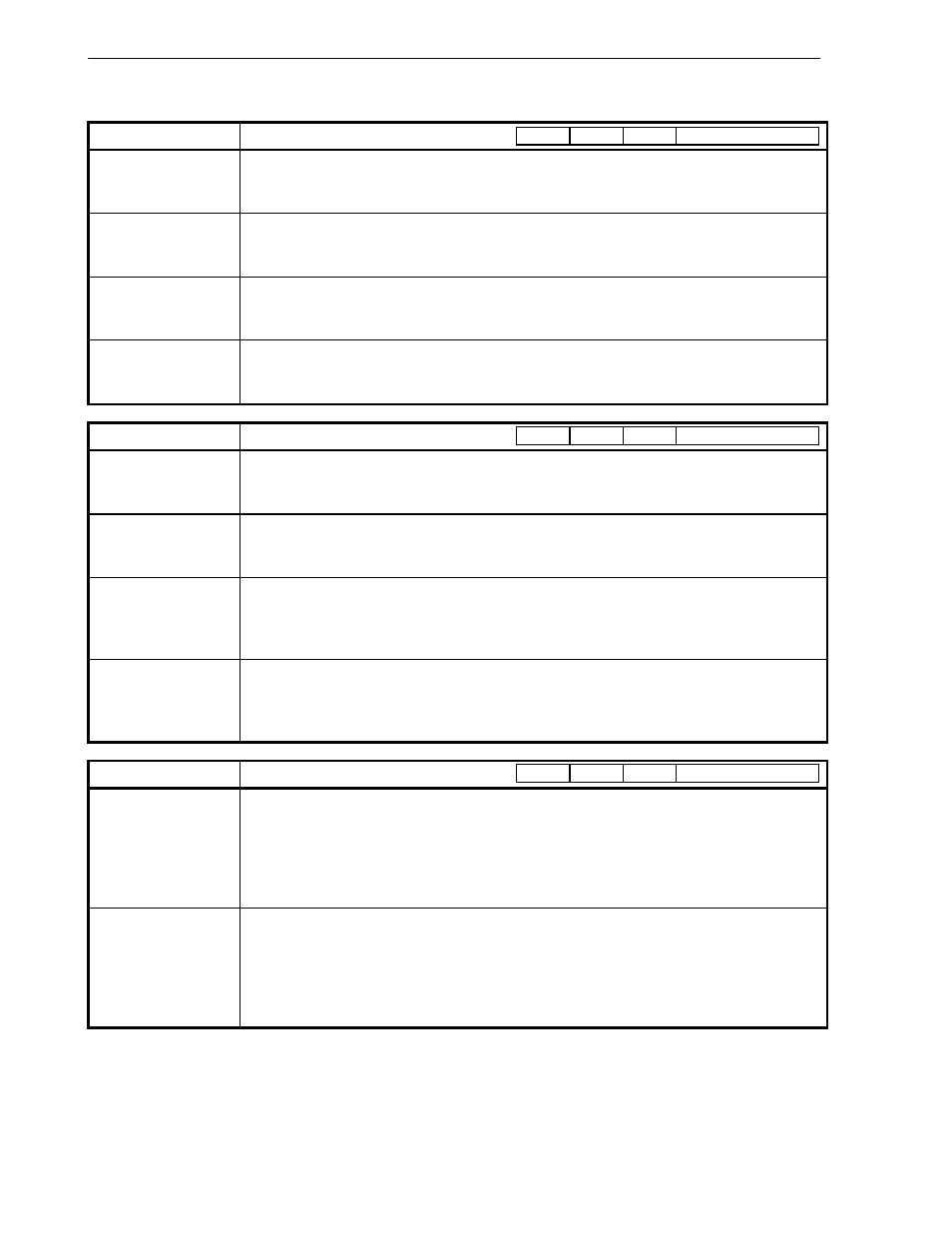

Table 2-18. Branch Instructions (Extended ISA)

Instruction

Format and Description

Branch On Equal Likely

BEQL rs, rt, offset

If the contents of register rs are equal to that of register rt, the program branches to the target address.

If the branch condition is not met, the instruction in the delay slot is discarded.

Branch On Not Equal

Likely

BNEL rs, rt, offset

If the contents of register rs are not equal to that of register rt, the program branches to the target

address. If the branch condition is not met, the instruction in the delay slot is discarded.

Branch On Less Than

Or Equal To Zero Likely

BLEZL rs, offset

If the contents of register rs are less than or equal to zero, the program branches to the target address.

If the branch condition is not met, the instruction in the delay slot is discarded.

Branch On Greater

Than Zero Likely

BGTZL rs, offset

If the contents of register rs are greater than zero, the program branches to the target address. If the

branch condition is not met, the instruction in the delay slot is discarded.

Instruction

Format and Description

Branch On Less Than

Zero Likely

BLTZL rs, offset

If the contents of register rs are less than zero, the program branches to the target address. If the

branch condition is not met, the instruction in the delay slot is discarded.

Branch On Greater

Than Or Equal To Zero

Likely

BGEZL rs, offset

If the contents of register rs are greater than or equal to zero, the program branches to the target

address. If the branch condition is not met, the instruction in the delay slot is discarded.

Branch On Less Than

Zero And Link Likely

BLTZALL rs, offset

The address of the instruction that follows delay slot is stored to register r31 (link register).

If the contents of register rs are less than zero, the program branches to the target address. If the

branch condition is not met, the instruction in the delay slot is discarded.

Branch On Greater

Than Or Equal To Zero

And Link Likely

BGEZALL rs, offset

The address of the instruction that follows delay slot is stored to register r31 (link register).

If the contents of register rs are greater than or equal to zero, the program branches to the target

address. If the branch condition is not met, the instruction in the delay slot is discarded.

Instruction

Format and Description

Branch On

Coprocessor 0 True

Likely

BC0TL offset

Adds the 16-bit offset (shifted left by two bits and sign extended to 32 bits) to the address of the

instruction in the delay slot to calculate the branch target address.

If the conditional signal of the coprocessor 0 is true, the program branches to the target address with

one-instruction delay.

If the branch condition is not met, the instruction in the delay slot is discarded.

Branch On

Coprocessor 0 False

Likely

BC0FL offset

Adds the 16-bit offset (shifted left by two bits and sign extended to 32 bits) to the address of the

instruction in the delay slot to calculate the branch target address.

If the conditional signal of the coprocessor 0 is false, the program branches to the target address with

one-instruction delay.

If the branch condition is not met, the instruction in the delay slot is discarded.

op

rs

rt

offset

REGIMM

offset

rs

sub

COP0

offset

BC

br