A.6 cpu instruction opcode bit encoding – NEC Network Controller uPD98502 User Manual

Page 588

APPENDIX A MIPS III INSTRUCTION SET DETAILS

588

Preliminary User’s Manual S15543EJ1V0UM

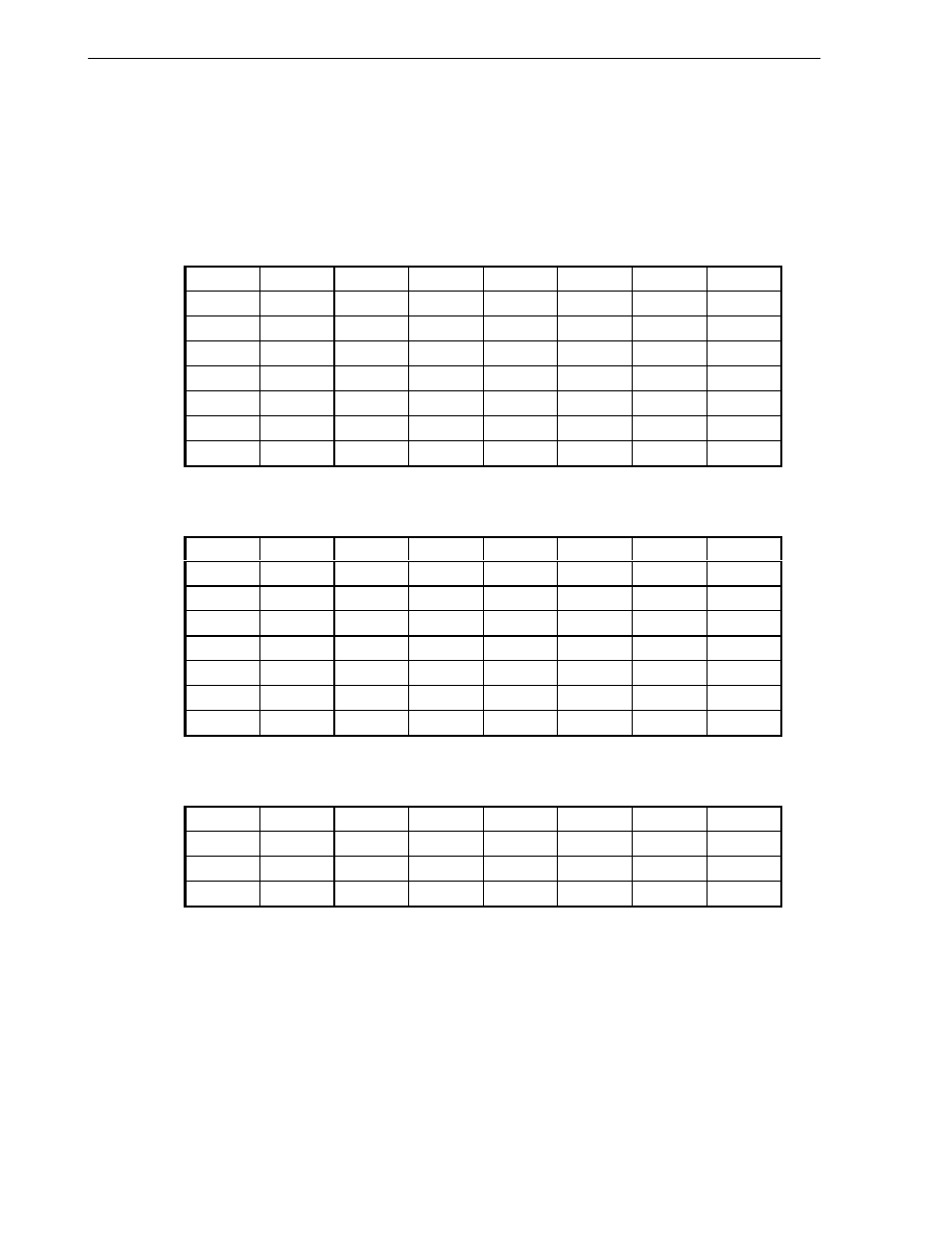

A.6 CPU Instruction Opcode Bit Encoding

Figure A-1 lists the V

R

4120A Opcode Bit Encoding.

Figure A-1. V

R

4120A Opcode Bit Encoding (1/2)

28...26

Opcode

31...29

0

1

2

3

4

5

6

7

0

SPECIAL

REGIMM

J

JAL

BEQ

BNE

BLEZ

BGTZ

1

ADDI

ADDIU

SLTI

SLTIU

ANDI

ORI

XORI

LUI

2

COP0

π

π

*

BEQL

BNEL

BLEZL

BGTZL

3

DADDI

ε

DADDIU

ε

LDL

ε

LDR

ε

*

JALX

θ

*

*

4

LB

LH

LWL

LW

LBU

LHU

LWR

LWU

ε

5

SB

SH

SWL

SW

SDL

ε

SDR

ε

SWR

CACHE

δ

6

*

π

π

*

*

π

π

LD

ε

7

*

π

π

*

*

π

π

SD

ε

2...0

SPECIAL function

5...3

0

1

2

3

4

5

6

7

0

SLL

*

SRL

SRA

SLLV

*

SRLV

SRAV

1

JR

JALR

*

*

SYSCALL

BREAK

*

SYNC

2

MFHI

MTHI

MFLO

MTLO

DSLLV

ε

*

DSRLV

ε

DSRAV

ε

3

MULT

MULTU

DIV

DIVU

DMULT

ε

DMULTU

ε

DDIV

ε

DDIVU

ε

4

ADD

ADDU

SUB

SUBU

AND

OR

XOR

NOR

5

MACC

DMACC

SLT

SLTU

DADD

ε

DADDU

ε

DSUB

ε

DSUBU

ε

6

TGE

TGEU

TLT

TLTU

TEQ

*

TNE

*

7

DSLL

ε

*

DSRL

ε

DSRA

ε

DSLL32

ε

*

DSRL32

ε

DSRA32

ε

18...16

REGIMM rt

20...19

0

1

2

3

4

5

6

7

0

BLTZ

BGEZ

BLTZL

BGEZL

*

*

*

*

1

TGEI

TGEIU

TLTI

TLTIU

TEQI

*

TNEI

*

2

BLTZAL

BGEZAL

BLTZALL

BGEZALL

*

*

*

*

3

*

*

*

*

*

*

*

*