11 instruction pipeline, 2 mips iii instruction set summary, 1 mips iii isa instruction formats – NEC Network Controller uPD98502 User Manual

Page 66

CHAPTER 2 V

R

4120A

66

Preliminary User’s Manual S15543EJ1V0UM

2.1.11 Instruction pipeline

The V

R

4120A has a 6-stage instruction pipeline. Under normal circumstances, one instruction is issued each

cycle.

A detailed description of pipeline is provided in Section 2.3 Pipeline.

2.2 MIPS III Instruction Set Summary

This section is an overview of the MIPS III ISA central processing unit (CPU) instruction set; refer to APPENDIX A

MIPS III INSTRUCTION SET DETAILS for detailed descriptions of individual CPU instructions.

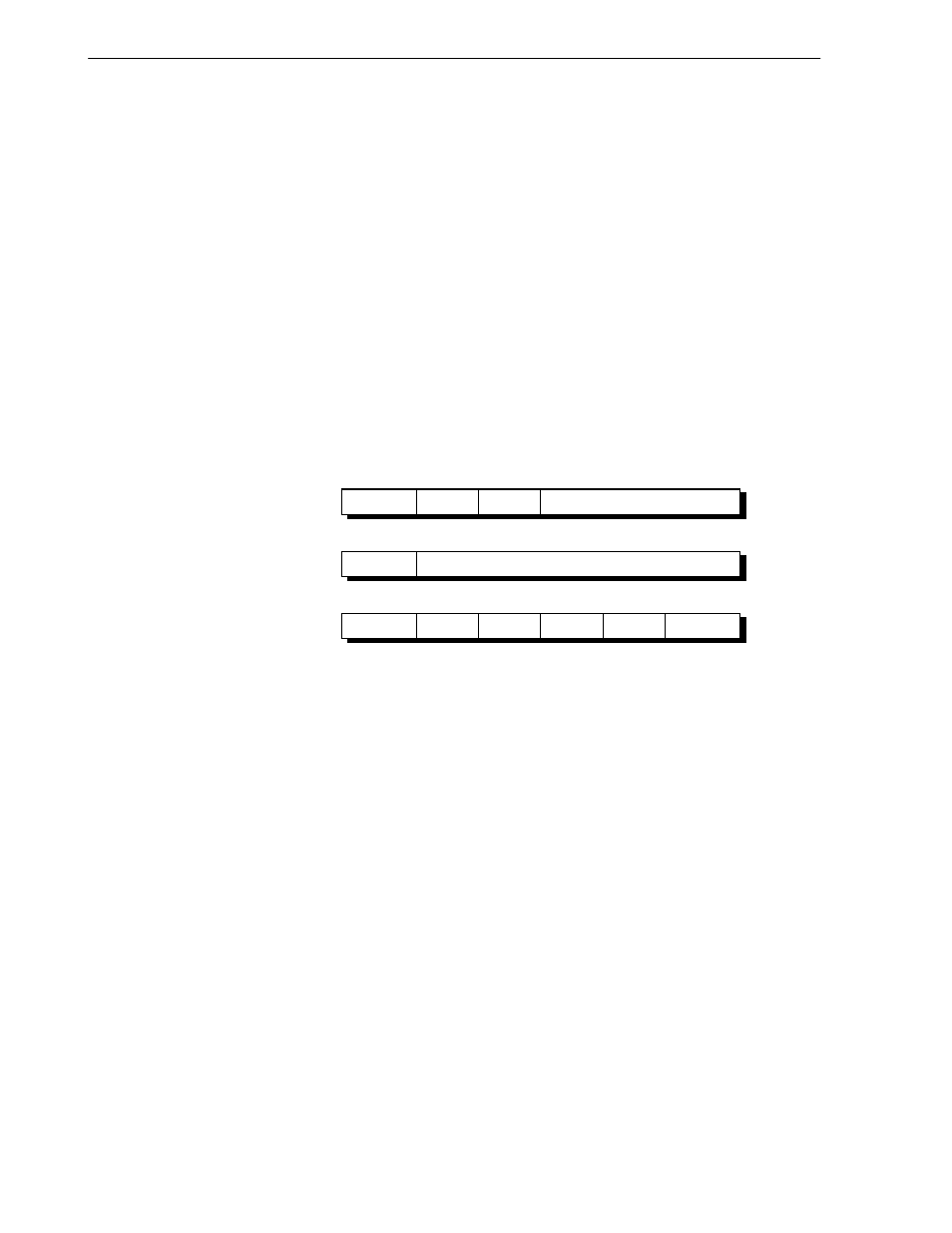

2.2.1 MIPS III ISA instruction formats

Each MIPS III ISA CPU instruction consists of a single 32-bit word, aligned on a word boundary. There are three

instruction formats - immediate (I-type), jump (J-type), and register (R-type) - as shown in Figure 2-8. The use of a

small number of instruction formats simplifies instruction decoding, allowing the compiler to synthesize more

complicated and less frequently used instruction and addressing modes from these three formats as needed.

Figure 2-8. MIPS III ISA CPU Instruction Formats

I-type (immediate)

op

0

15

16

20

21

25

26

31

J-type (jump)

op

target

0

25

26

31

R-type (register)

immediate:

funct:

sa:

rd:

target:

6-bit function field

5-bit shift amount

5-bit destination register specifier

26-bit unconditional branch target address

16-bit immediate value, branch displacement, or

address displacement

5-bit target (source/destination) register specifier or

branch condition

6-bit operation code

5-bit source register specifier

rt:

rs:

op:

op

0

15

16

20

21

25

26

31

5

6

10

11

rs

rt

immediate

rs

rt

rd

sa

funct

2.2.1.1 Support of the MIPS ISA

The V

R

4120A CORE does not support a multiprocessor operating environment. Thus the synchronization support

instructions defined in the MIPS II and MIPS III ISA - the load linked and store conditional instructions - cause

reserved instruction exception. The load/link (LL) bit is eliminated.

Caution

That the SYNC instruction is handled as a NOP instruction since all load/store instructions in

this processor are executed in program order.