NEC Network Controller uPD98502 User Manual

Page 594

APPENDIX B V

R

4120A COPROCESSOR 0 HAZARDS

594

Preliminary User’s Manual S15543EJ1V0UM

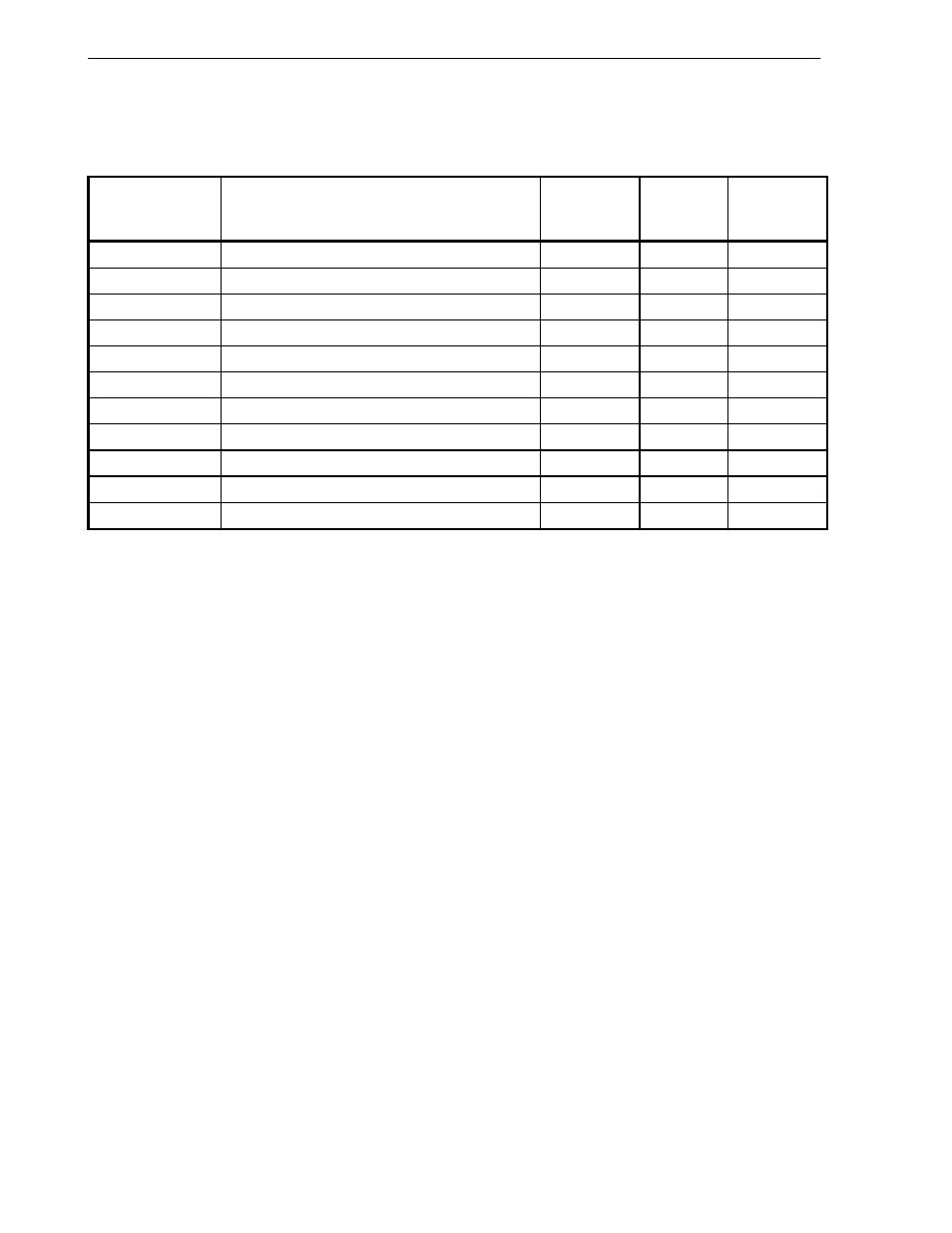

Table B-2 indicates examples of calculation.

Table B-2. Calculation Example of CP0 Hazard and Number of Instructions Inserted

Destination

Source

Contending

Internal

Resource

Number of

Instructions

Inserted

Formula

TLBWR/TLBWI

TLBP

TLB Entry

2

5 – (2 + 1)

TLBWR/TLBWI

Load or Store using newly modified TLB

TLB Entry

1

5 – (3 + 1)

TLBWR/TLBWI

Instruction fetch using newly modified TLB

TLB Entry

2

5 – (2 + 1)

MTC0, Status [CU]

Coprocessor instruction that requires the setting of CU

Status [CU]

2

5 – (2 + 1)

TLBR

MFC0 EntryHi

EntryHi

1

5 – (3 + 1)

MTC0 EntryLo0

TLBWR/TLBWI

EntryLo0

2

5 – (2 + 1)

TLBP

MFC0 Index

Index

2

6 – (3 + 1)

MTC0 EntryHi

TLBP

EntryHi

2

5 – (2 + 1)

MTC0 EPC

ERET

EPC

2

5 – (2 + 1)

MTC0 Status

ERET

Status

2

5 – (2 + 1)

MTC0 Status [IE]

Note

Instruction that causes an interrupt

Status [IE]

2

5 – (2 + 1)

Note The number of hazards is undefined if the instruction execution sequence is changed by exceptions. In

such a case, the minimum number of hazards until the IE bit value is confirmed may be the same as the

maximum number of hazards until an interrupt request occurs that is pending and enabled.