NEC Network Controller uPD98502 User Manual

Page 71

CHAPTER 2 V

R

4120A

Preliminary User’s Manual S15543EJ1V0UM

71

2.2.2.2 Computational instructions

Computational instructions perform arithmetic, logical, and shift operations on values in registers. Computational

instructions can be either in register (R-type) format, in which both operands are registers, or in immediate (I-type)

format, in which one operand is a 16-bit immediate.

Computational instructions are classified as:

(1) ALU immediate instructions

(2) Three-operand type instructions

(3) Shift instructions

(4) Multiply/divide instructions

To maintain data compatibility between the 64- and 32-bit modes, it is necessary to sign-extend 32-bit operands

correctly. If the sign extension is not correct, the 32-bit operation result is meaningless.

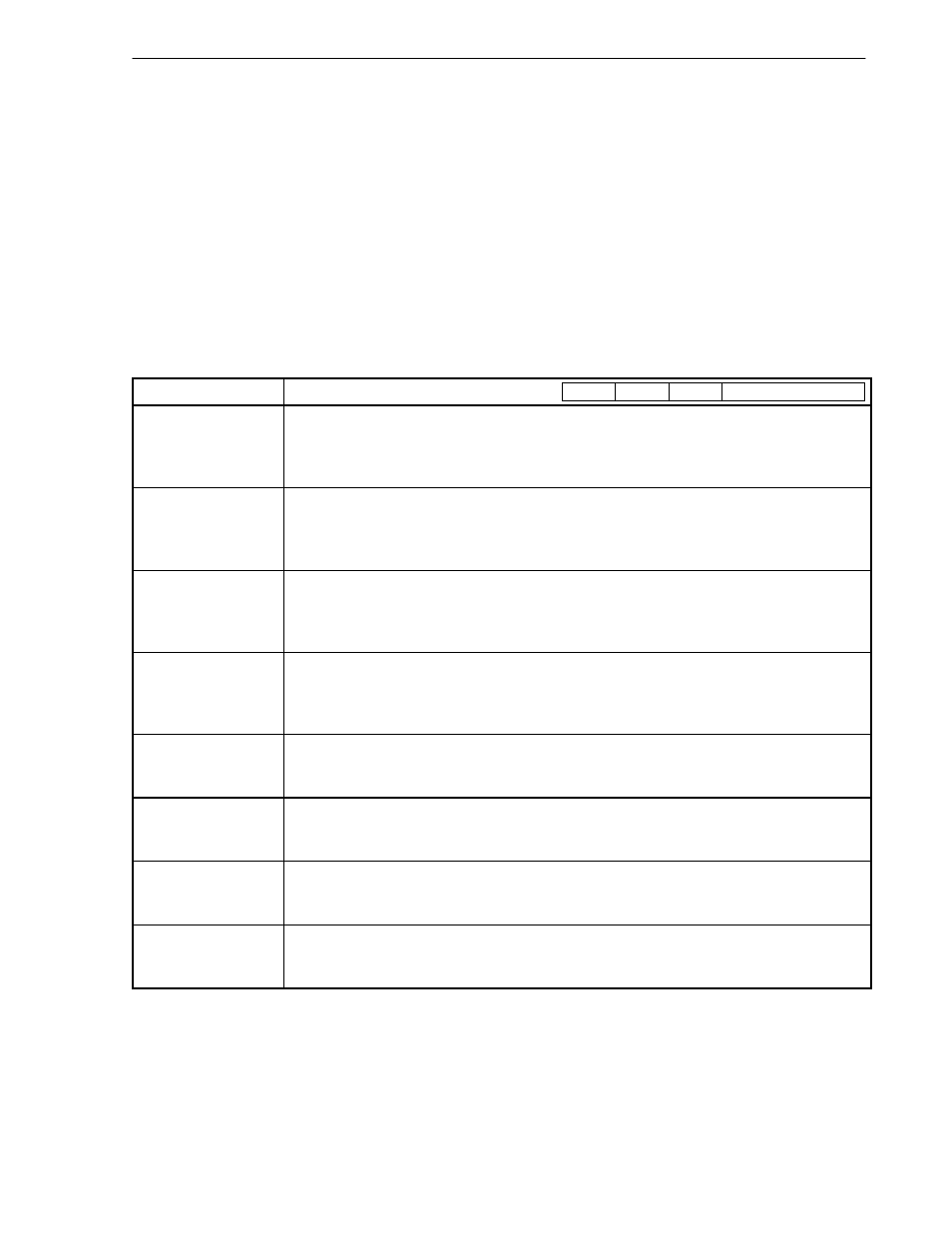

Table 2-6. ALU Immediate Instruction

Instruction

Format and Description

Add Immediate

ADDI rt, rs, immediate

The 16-bit immediate is sign extended and then added to the contents of register rs to form a 32-bit

result. The result is stored into register rt. In the 64-bit mode, the operand must be sign extended.

An exception occurs on the generation of 2's complement overflow.

Add Immediate

Unsigned

ADDIU rt, rs, immediate

The 16-bit immediate is sign extended and then added to the contents of register rs to form a 32-bit

result. The result is stored into register rt. In the 64-bit mode, the operand must be sign extended. No

exception occurs on the generation of integer overflow.

Set On Less Than

Immediate

SLTI rt, rs, immediate

The 16-bit immediate is sign extended and then compared to the contents of register rt treating both

operands as signed integers. If rs is less than the immediate, the result is set to 1; otherwise, the

result is set to 0. The result is stored to register rt.

Set On Less Than

Immediate Unsigned

SLTIU rt, rs, immediate

The 16-bit immediate is sign extended and then compared to the contents of register rt treating both

operands as unsigned integers. If rs is less than the immediate, the result is set to 1; otherwise, the

result is set to 0. The result is stored to register rt.

And Immediate

ANDI rt, rs, immediate

The 16-bit immediate is zero extended and then ANDed with the contents of the register. The result is

stored into register rt.

Or Immediate

ORI rt, rs, immediate

The 16-bit immediate is zero extended and then ORed with the contents of the register. The result is

stored into register rt.

Exclusive Or Immediate

XORI rt, rs, immediate

The 16-bit immediate is zero extended and then Ex-ORed with the contents of the register. The result

is stored into register rt.

Load Upper Immediate

LUI rt, immediate

The 16-bit immediate is shifted left by 16 bits to set the lower 16 bits of word to 0. The result is stored

into register rt. In the 64-bit mode, the operand must be sign extended.

op

rs

rt

immediate