8 u_ep0cr (usb ep0 control register) – NEC Network Controller uPD98502 User Manual

Page 320

CHAPTER 6 USB CONTROLLER

320

Preliminary User’s Manual S15543EJ1V0UM

6.2.8

U_EP0CR (USB EP0 Control Register)

This register is used for setting the operation of EndPoint0.

If the value in the MAXP field is rewritten during transmitting or receiving operation, the operation of USB Controller

may become unpredictable. Therefore, the MAXP can be written only when initial setting is being performed.

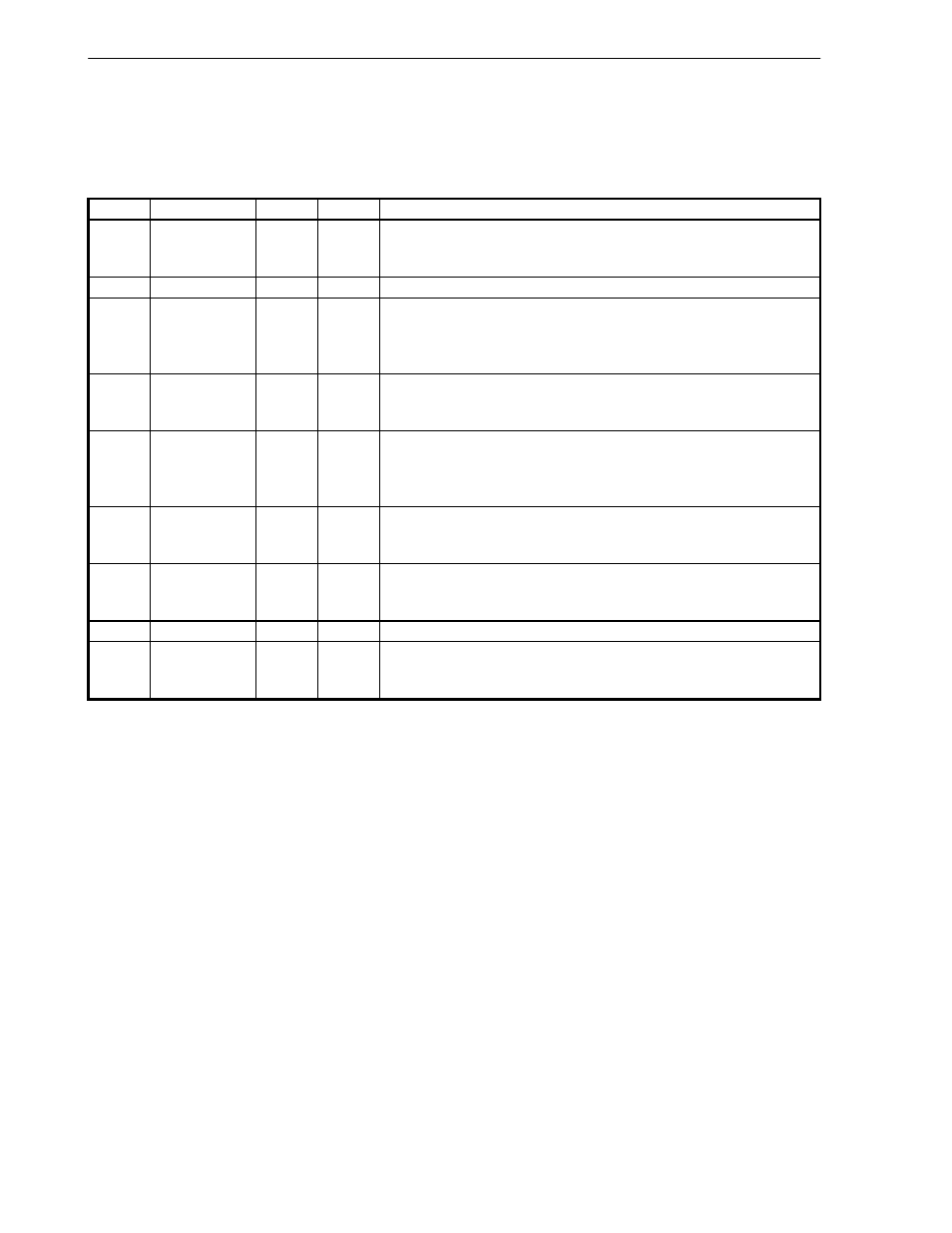

Bits

Field

R/W

Default

Description

31

EP0EN

R/W

0

EndPoint Enable:

When the V

R

4120A sets this bit to a ‘1’, EndPoint0 is enabled for transmitting

and receiving data to and from USB.

30:19

Reserved

R/W

0

Reserved for future use. Writes ‘0’s.

20

ISS

R/W

0

IN Transmit Stall:

When the V

R

4120A sets this bit to a ‘1’, a STALL packet is sent at the Data

Phase.

Receiving a SETUP packet causes this bit to be a ‘0’.

19

INAK

R/W

0

IN NAK:

When the V

R

4120A sets this bit to a ‘1’, a NAK packet is sent at the Data

Phase.

18

OSS

R/W

0

OUT Transmit Stall:

When the V

R

4120A sets this bit to a ‘1’, a STALL handshake is performed at

the Handshake Phase.

Receiving a SETUP packet causes this bit to be a ‘0’

17

NHSK0

R/W

0

No Handshake:

When the V

R

4120A sets this bit to a ‘1’, No Handshake is performed at the

Handshake Phase.

16

ONAK

R/W

0

OUT NAK:

When the V

R

4120A sets this bit to a ‘1,’ NAK Handshake is performed at the

Handshake Phase.

15:7

Reserved

R/W

0

Reserved for future use. Writes ‘0’s.

6:0

MAXP0

R/W

0

MAX Packet size:

The Max Packet Size for EndPoint0. Prior to the start of a USB transaction,

the V

R

4120A must set an appropriate value into this register.

Remark

When a STALL handshake is sent by a control endpoint in either the Data or Status stage of a control

transfer, a STALL handshake must be returned on all succeeding access to that endpoint until a SETUP

PID is received. The endpoint is not required to return a STALL handshake after it receives a subsequent

SETUP PID (referred from USB1.1 Specification).