6 program compatibility – NEC Network Controller uPD98502 User Manual

Page 100

CHAPTER 2 V

R

4120A

100

Preliminary User’s Manual S15543EJ1V0UM

2.3.6 Program compatibility

The V

R

4120A core is designed taking into consideration program compatibility with other V

R

-Series processors.

However, because the V

R

4120A differs from other processors in its architecture, it may not be able to run some

programs that run on other processors. Likewise, programs that run on the V

R

4120A will not necessarily run on other

processors. Matters which should be paid attention to when porting programs between the V

R

4120A core and other

V

R

-Series processors are listed below.

• The V

R

4120A core does not support floating-point instructions since it has no Floating-Point Unit (FPU).

• Multiply-add instructions (DMACC, MACC) are added in the V

R

4120A.

• Instructions for power modes (HIBERNATE, STANDBY, SUSPEND) are added in the V

R

4120A to support

power modes.

• The V

R

4120A does not have the LL bit to perform synchronization of multiprocessing. Therefore, the CPU

core does not support instructions which manipulate the LL bit (LL, LLD, SC, SCD).

• A 16-bit length MIPS16 instruction set is added in the V

R

4120A (but the

µPD98502 does not support MIPS16

mode).

• The CP0 hazards of the V

R

4120A are equally or less stringent than those of other processors (for details, see

APPENDIX B V

R

4120A COPROCESSOR 0 HAZARDS).

• An instruction for debug has been added for the V

R

4120A. However, this instruction cannot be used for the

V

R

4120A.

For more information, refer to APPENDIX A MIPS III INSTRUCTION SET DETAILS, the V

R

4100, V

R

4111™

User's Manual, or the V

R

4300

User's Manual.

The list of instructions supported by V

R

-Series products is shown below.

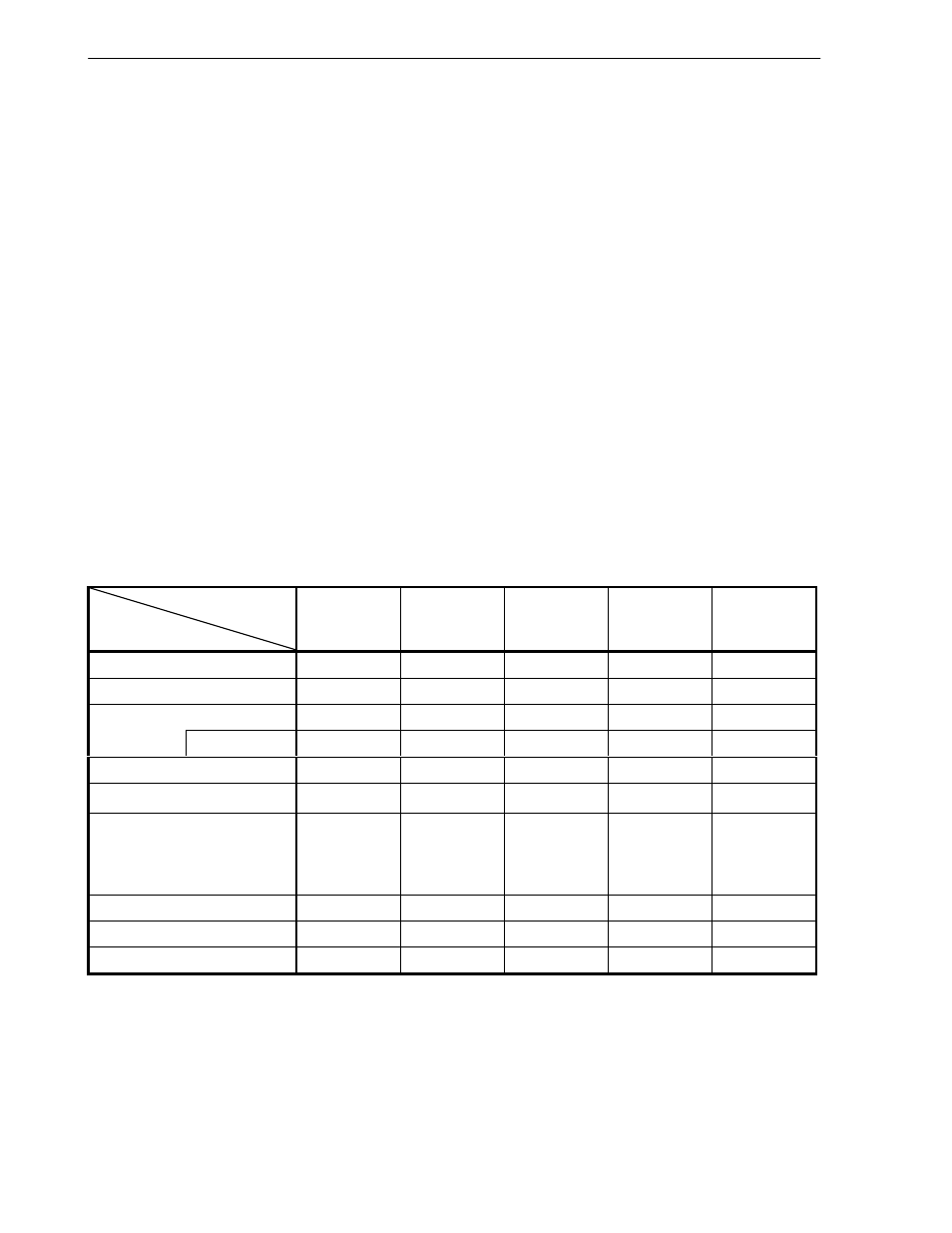

Table 2-26. V

R

Series Supported Instructions

Product

Instruction

V

R

4100

V

R

4102™

V

R

4111

V

R

4120A

Core

V

R

4300

V

R

4305™

V

R

4310™

V

R

5000™

V

R

10000™

MIPS I instruction set

Ο

Ο

Ο

Ο

Ο

MIPS II instruction set

Ο

Ο

Ο

Ο

Ο

MIPS III instruction set

Ο

Ο

Ο

Ο

Ο

LL bit operation

Ч

Ч

Ч

Ο

Ο

MIPS IV instruction set

Ч

Ч

Ч

Ч

Ο

MIPS16 instruction set

×

Ο

Ο

Note

Ч

Ч

16-bit multiply-add operation

Ο

Ο

Ο

(Use of 32-bit

multiply-add

operation

Ч

Ч

32-bit multiply-add operation

Ч

Ч

Ο

Ч

Ч

Floating-point operation

Ч

Ч

Ч

Ο

Ο

Power mode transfer

Ο

Ο

Ο

Ч

Ч

Note The

µPD98502 does not support MIPS16 mode. The MIPD16EN pin (located at D11) should be connected to

GND.