NEC Network Controller uPD98502 User Manual

Page 125

CHAPTER 2 V

R

4120A

Preliminary User’s Manual S15543EJ1V0UM

125

2.4.5.9 Load linked address (LLAddr) register (17)

The read/write Load Linked Address (LLAddr) register is not used with the V

R

4120A processor except for

diagnostic purpose, and serves no function during normal operation.

LLAddr register is implemented just for compatibility between the V

R

4120A and V

R

4000/V

R

4400

.

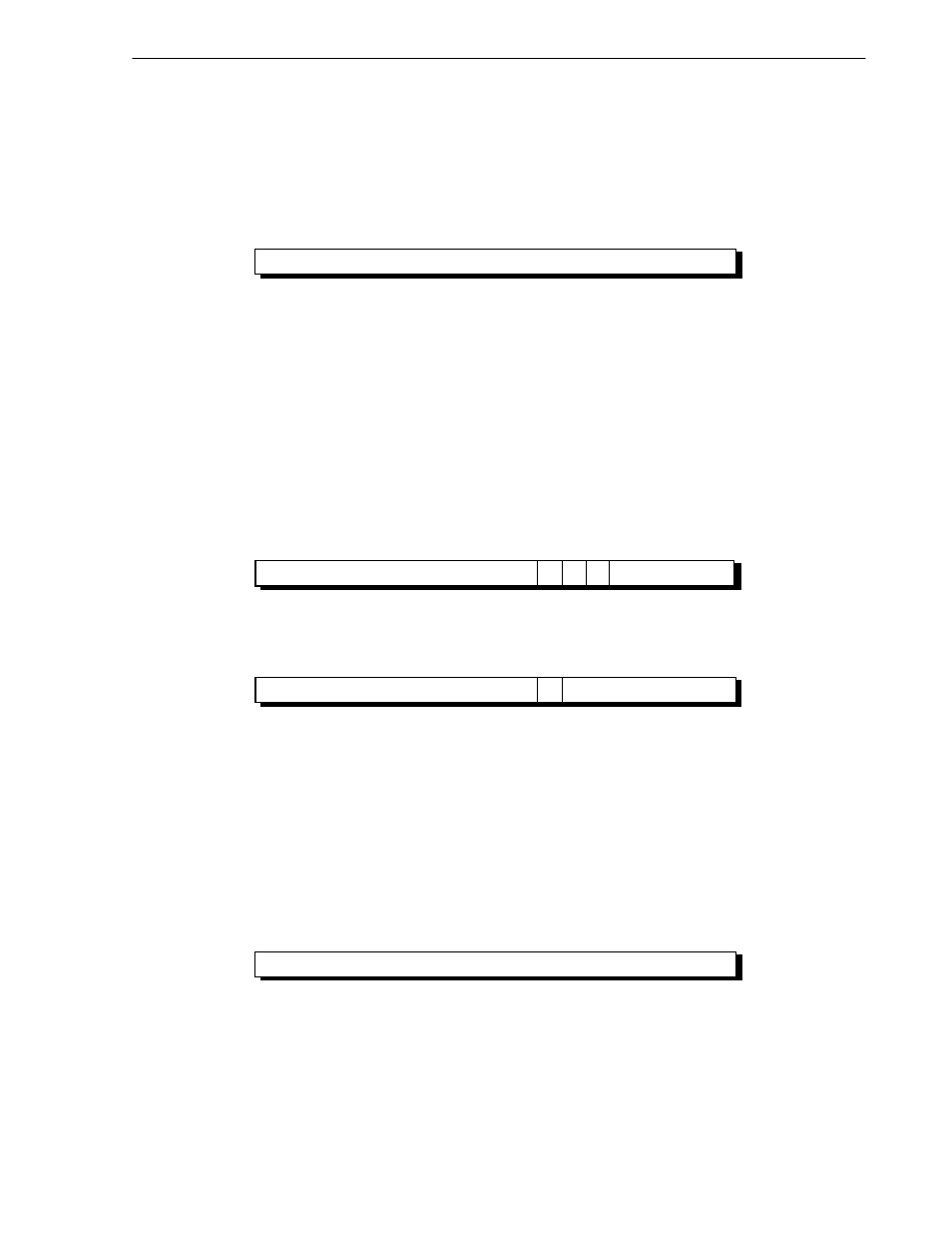

Figure 2-43. LLAddr Register

0

31

PAddr

32

PAddr: 32-bit physical address

2.4.5.10 Cache tag registers (TagLo (28) and TagHi (29))

The TagLo and TagHi registers are 32-bit read/write registers that hold the primary cache tag during cache

initialization, cache diagnostics, or cache error processing. The Tag registers are written by the CACHE and MTC0

instructions.

Figures 2-44 and 2-45 show the format of these registers.

Figure 2-44. TagLo Register

(a) When used with data cache

22

0

31

10

9

8

7

6

PTagLo

(b) When used with instruction cache

V

D

W

0

1

1

1

7

22

0

31

10

9

8

PTagLo

V

0

1

9

PTagLo: Specifies physical address bits 31 to 10.

V

: Valid bit

D

: Dirty bit. However, this bit is defined only for the compatibility with the V

R

4000 Series processors, and

does not indicate the status of cache memory in spite of its readability and writability. This bit cannot

change the status of cache memory.

W

: Write-back bit (set if cache line has been updated)

0

: RFU. Write 0 in a write operation. When this field is read, 0 is read.

Figure 2-45. TagHi Register

0

31

0

32

0: RFU. Write 0 in a write operation. When this field is read, 0 is read.