Dmult, Doubleword multiply – NEC Network Controller uPD98502 User Manual

Page 482

APPENDIX A MIPS III INSTRUCTION SET DETAILS

482

Preliminary User’s Manual S15543EJ1V0UM

DMULT

Doubleword Multiply

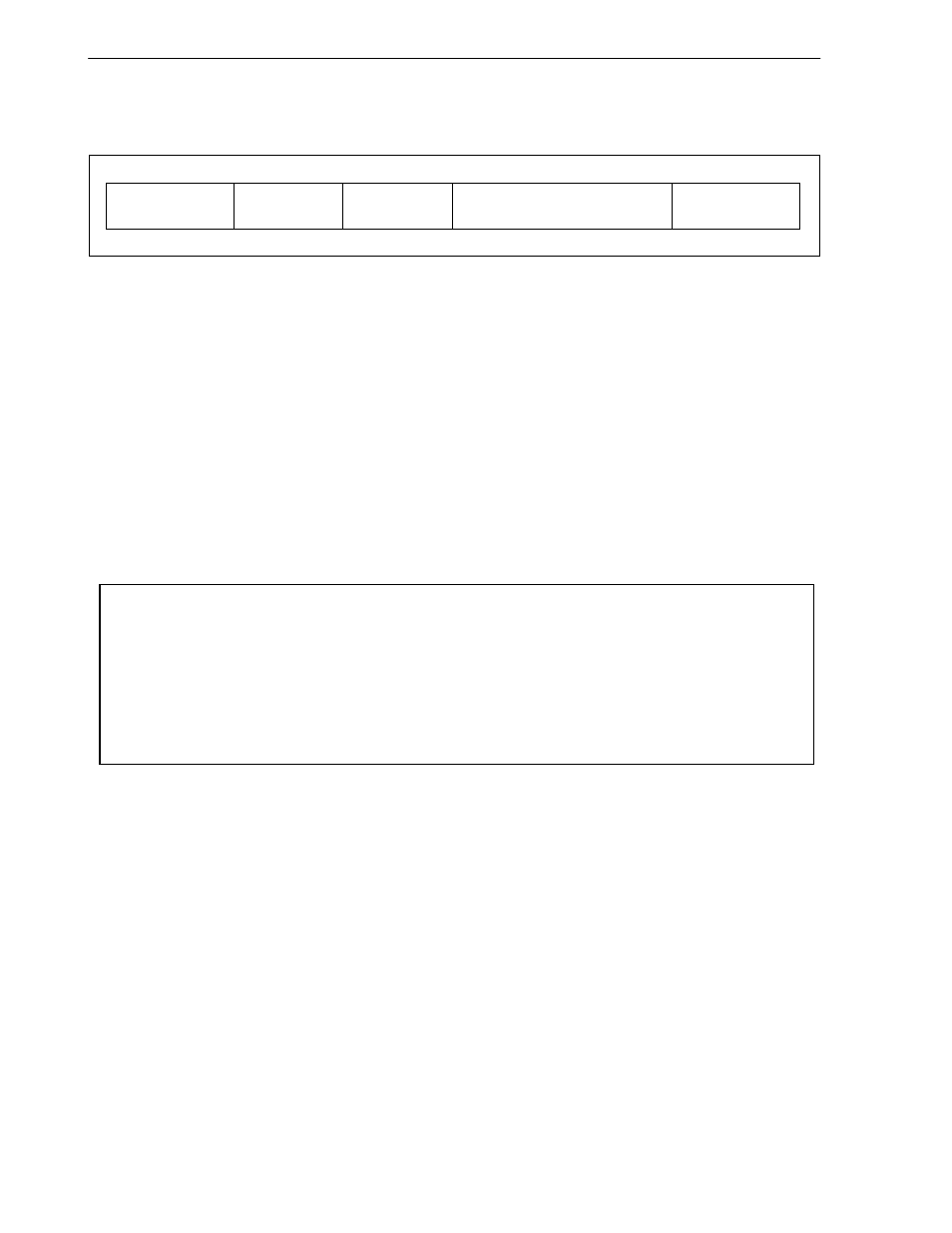

DMULT

rs

SPECIAL

0 0 0 0 0 0

rt

0

0 0 0 0 0 0 0 0 0 0

31

26 25

21 20

16 15

0

6

5

5

10

DMULT

0 1 1 1 0 0

6 5

6

Format:

DMULT rs, rt

Description:

The contents of general registers

rs and rt are multiplied, treating both operands as 2’s complement values. No

integer overflow exception occurs under any circumstances.

When the operation completes, the low-order word of the double result is loaded into special register

LO, and the

high-order word of the double result is loaded into special register

HI.

If either of the two preceding instructions is MFHI or MFLO, the results of these instructions are undefined. Correct

operation requires separating reads of

HI or LO from writes by a minimum of two other instructions.

This operation is defined in 64-bit mode or in 32-bit kernel mode. Execution of this instruction in 32-bit user or

supervisor mode causes a reserved instruction exception.

Operation:

64

T-2:

LO

← undefined

HI

← undefined

T-1:

LO

← undefined

HI

← undefined

T:

t

← GPR [rs]

*

GPR [rt]

LO

← t

63..0

HI

← t

127..64

Exceptions:

Reserved instruction exception (32-bit user mode/supervisor mode)