NEC Network Controller uPD98502 User Manual

Page 409

CHAPTER 7 PCI CONTROLLER

Preliminary User’s Manual S15543EJ1V0UM

409

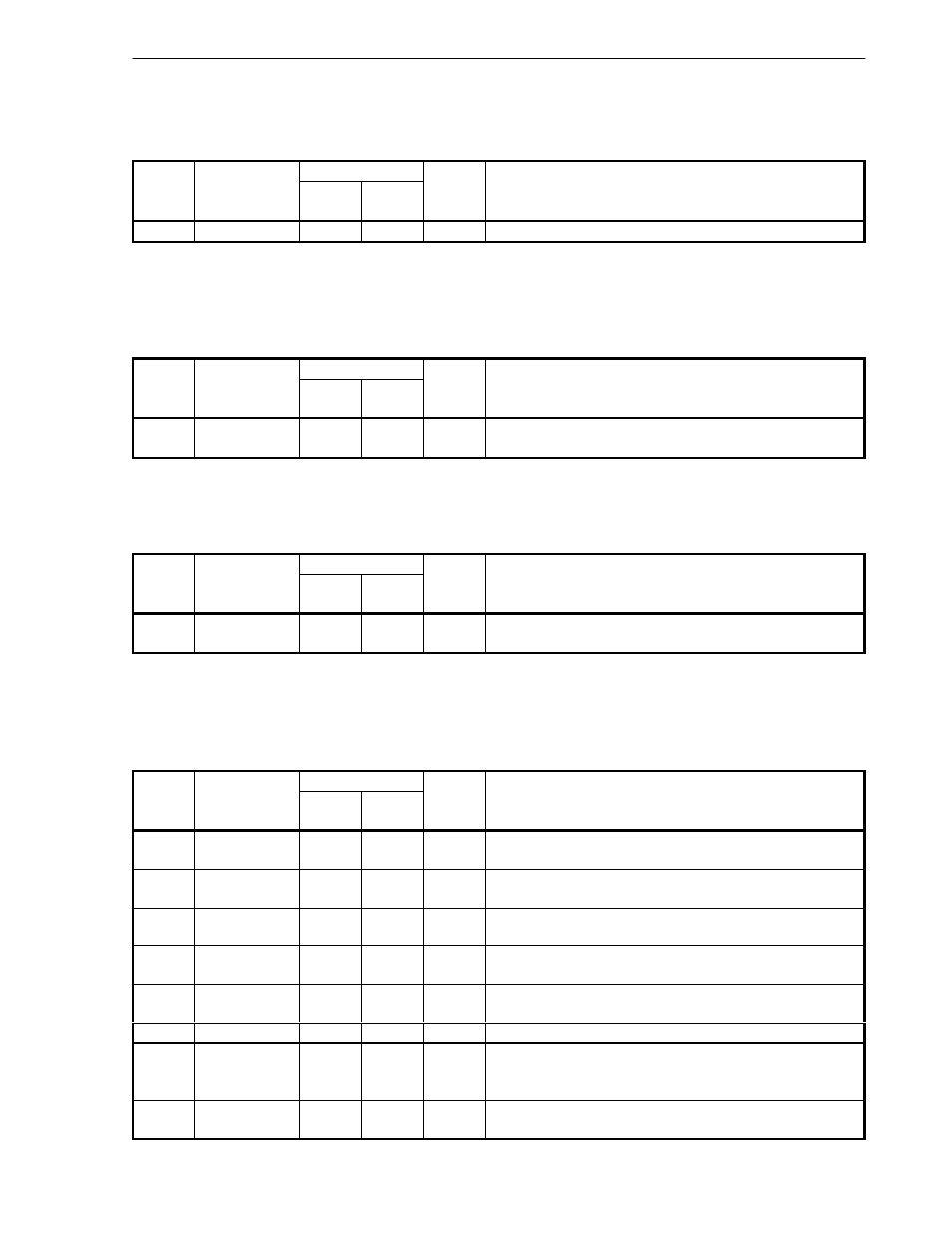

7.5.19.19 Max_Lat register

This register specifies how often the device needs to get the PCI bus usage.

R/W

Bits

Field

Internal

bus

PCI

Default

Description

7:0

Max_Lat

R/W

R

0

The value should be set by the V

R

4120A.

7.5.19.20 Cap_ID register

This register indicates what kind of data structure of the capability is pointed to. The value ‘01H’ means that the

data structure is for the PCI Power Management.

R/W

Bits

Field

Internal

bus

PCI

Default

Description

7:0

Cap_ID

R

R

01H

Hardwired to ‘01H’, that identifies the linked list item as being the

PCI Power Management registers.

7.5.19.21 Next_Item_Ptr register

This register points the next item in the capabilities list. NULL means that this item is the last one in the list.

R/W

Bits

Field

Internal

bus

PCI

Default

Description

7:0

Next_Item_Ptr

R

R

0

Hardwired to ‘00H’, because the PPMI function is the last item in

the capabilities list for The PCI Controller.

7.5.19.22 PMC register

The Power Management Capabilities register provides information on the capabilities of the function related to

power management.

R/W

Bits

Field

Internal

bus

PCI

Default

Description

15:11

PME_Support

R/W

R

0

The V

R

4120A should set the bits of the power state in which the

chip supports PME_B assertion.

10

D2_Support

R

R

0

Hardwired to a ‘0’, because the PCI Controller does not support

D2 state.

9

D1_Support

R/W

R

0

If the chip supports D1 state, this bit should be set by the

V

R

4120A.

8:6

Aux_Current

R

R

000

Hardwired to ‘000’, because the PCI Controller does not support

PME# from D3cold state.

5

DSI

R

R

0

Hardwired to a ‘0’, because the PCI Controller does not require

the special initialization.

4

Reserved

R

R

0

Hardwired to a ‘0’.

3

PME Clock

R/W

R

0

Indicating Whether PCI clock is required or not, in order to

generate PME_B. PME_B is generated using an 66MHz internal

clock. The V

R

4120A must set a ‘1’ to this bit.

2:0

Version

R

R

010

Hardwired to ‘010’, which indicates that the PCI Controller

complies with Revision 1.1 of the PPMI.