5 coprocessors (cp0) – NEC Network Controller uPD98502 User Manual

Page 63

CHAPTER 2 V

R

4120A

Preliminary User’s Manual S15543EJ1V0UM

63

2.1.5 Coprocessors (CP0)

MIPS ISA defines 4 types of coprocessors (CP0 to CP3).

• CP0 translates virtual addresses to physical addresses, switches the operating mode (kernel, supervisor, or

user mode), and manages exceptions. It also controls the cache subsystem to analyze a cause and to return

from the error state.

• CP1 is reserved for floating-point instructions.

• CP2 is reserved for future definition by MIPS.

• CP3 is no longer defined. CP3 instructions are reserved for future extensions.

Figure 2-7 shows the definitions of the CP0 register, and Table 2-1 shows simple descriptions of each register. For

the detailed descriptions of the registers related to the virtual system memory, refer to Section 2.4 Memory

Management System. For the detailed descriptions of the registers related to exception handling, refer to Section

2.5 Exception Processing.

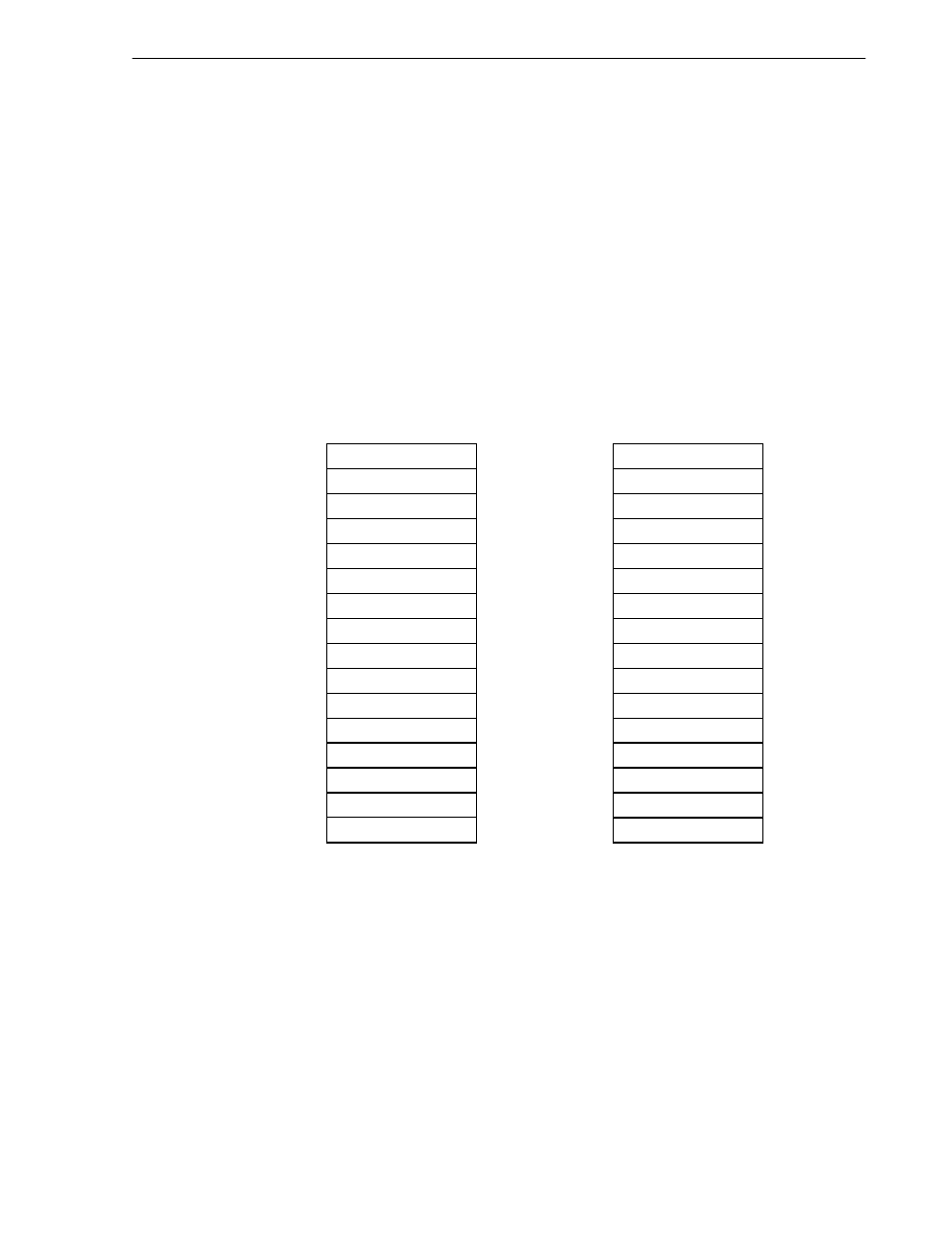

Figure 2-7. CP0 Registers

0

Notes 1. for Memory management

2. for Exception handling

Remark RFU: Reserved for future use

Register No.

Register name

Index

Note 1

1

Random

Note 1

2

EntryLo0

Note 1

3

EntryLo1

Note 1

4

Context

Note 2

5

PageMask

Note 1

6

Wired

Note 1

7

RFU

8

BadVAddr

Note 1

9

Count

Note 2

10

EntryHi

Note 1

11

Compare

Note 2

12

Status

Note 2

13

Cause

Note 2

14

EPC

Note 2

15

PRId

Note 1

16

Register No.

Register name

Config

Note 1

17

LLAddr

Note 1

18

WatchLo

Note 2

19

WatchHi

Note 2

20

XContext

Note 2

21

RFU

22

RFU

23

RFU

24

RFU

25

RFU

26

PErr

Note 2

27

CacheErr

Note 2

28

TagLo

Note 1

29

TagHi

Note 1

30

ErrorEPC

Note 2

31

RFU